В прошлых занятиях мы проработали тему организации передачи данных по шине SPI в модуле MSSP.

Но мы также знаем, что кроме режима SPI наш модуль MSSP может работать аппаратно также и с шиной I2C.

Шина I2C (Inter-Integrated Circuit) — это шина, управляемая по двум проводам и по определённому протоколу. Данная шина является последовательной и асимметричной.

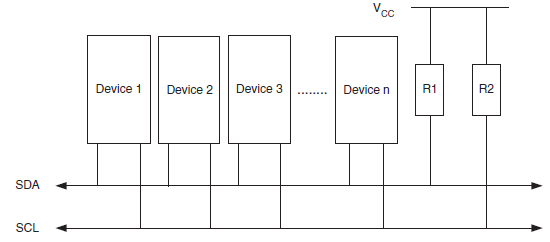

Для передачи данных шина I2C использует две двунаправленные линии связи (SDA и SCL). Применяется эта шина для соединения низкоскоростных периферийных компонентов с процессорами и микроконтроллерами (например, в мобильных телефонах, во встраиваемых системах, на материнских платах и т.д.).

Шина I2C распространена не меньше, чем шина SPI, так как она, хоть и не является такой скоростной, но зато она использует меньше проводов для соединения устройств, а, самое главное, за счёт использования адресов устройств, может обслуживать (конечно при создании всех условий) до 127 устройств на одном соединении.

Прежде, чем перейти к контроллеру, давайте немного разберёмся вообще с принципом работы шины I2C.

Как мы уже поняли, данный интерфейс предаёт данные по проводам. Причем именно по двум проводам

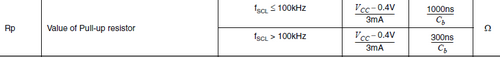

Как мы видим из данной блок-схемы, у нас есть два провода или контакта — SDA и SCL, подсоединённые к контроллеру к его соответствующим ножкам, а затем к этим проводам мы ещё подключаем какое-нибудь устройство или несколько устройств. Теоретически мы можем подключить до 127 устройств, впоследствии мы поймём, почему именно столько. Ножка SDA отвечает за передачу и приём данных по данной шине, а ножка SCL — это ножка тактирования, таким образом шина I2C является синхронной, что увеличивает стабильность и гарантированность передачи данных по ней. Также в данной блок-схеме мы наблюдаем то, что ещё к данным ножкам необходимо подтянуть резисторы на шину питания, причём как правило в каких-то модулях или устройствах данные резисторы уже подтянуты, и. если мы подключим их несколько, то у нас получится ряд параллельно подключенных подтягивающих резисторов, что будет очень нехорошо и придется оставить их в каком-то одном устройстве, а в других выпаять. Всё это происходит потому, что есть ограничение на номинал данных резисторов в зависимости от определенных условий

Как показала практика, данные резисторы не должны быть сопротивлением более 10 килоом и менее 4,7 килоом.

Также, само собой, сигналы должны быть толерантными к логическим уровням нашего МК, поэтому подключенные устройства должны быть соответствующим образом запитаны, а также общий провод устройств и контроллера также должен быть объединён.

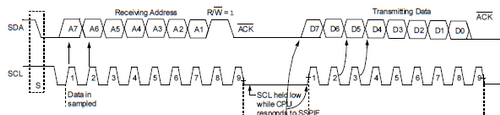

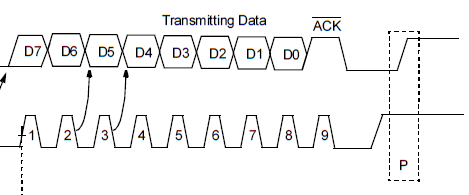

Сигнал передаётся следующим образом. Сначала обе линии (и данных и тактовая) находятся в высоком уровне за счёт подтягивающих к шине питания резисторов. При возникшем желании передать или принять данные, ведущее устройство на шине SDA формирует команду START с помощью притягивания шины SDA к земле (устанавливая низкий логический уровень). Вообщем, условие СТАРТ обеспечивается переходом шины SDA из высокого состояния в низкое. Затем с помощью той же шины SDA ведущее устройство передаёт 7-битный (а в некоторых случаях и 10-битный) адрес ведомого устройства, которому оно хочет передать или от которого хочет принять информацию. Соответственно, одновременно с передачей каждого бита данных ведущее устройство по шине SCL передаёт тактовые импульсы. Если на шине формируется бит «1», то шина находится в высоком уровне, а если «0», то в низком. Затем идёт ещё один бит, гласящий о том, хотим мы принять или передать информацию. Если мы хотим информацию принимать (читать), то передаём 1, если передавать (писать), то 0. А уж затем мы начинаем либо передавать либо принимать данные. Если ведущее устройство данные принимает, то оно продолжает тактирование и одновременно с этим на шине SDA начнут приходить данные. Если ведущее устройство данные передаёт, то оно само формирует импульсы данных на ножке SDA

По окончанию передачи данных ведущее устройство формирует условие (или команду) STOP, что обеспечивается, в отличие от команды START, переходом шины SDA из низкого состояния в высокое

То есть, если мы передали последний бит 1, то мы сначала перед условием STOP обязаны вернуть шину в нулевое состояние (притянуть к земле или к низкому уровню). Также помимо условий START и STOP существует возможность, а иногда и обязанность ведущего устройства, получить подтверждение от ведомого о принятии данных последним. Происходит подтверждение после приёма очередной порции данных (байта, слова и т.д.). Подтверждение обеспечивается притягиванием шины SDA к низкому уровню ведомым устройством. Ведущий отслеживает это, и обретает уверенность в том, что данные ведомый принял.

Вот так вот, вообщем, кратко, мы немного узнали о работе шины I2C. Я не хочу рисовать никакие диаграммы, так как их и так уже полно и в википедии, и на специальных тематических ресурсах, а также в различной технической документации. Мы лучше в процессе практической работы с шиной всё это отследим с помощью логического анализа шины.

Как же организована данная шина в контроллере PIC в его модуле MSSP?

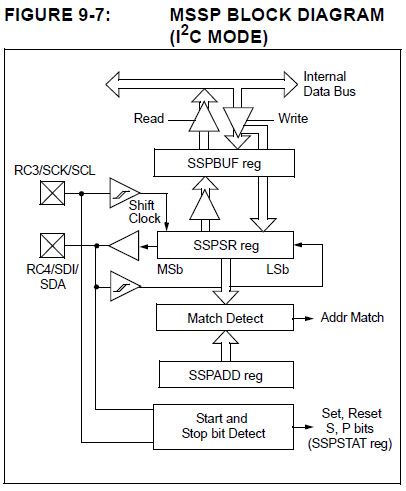

Чтобы ответить на этот вопрос (конечно очень кратко, нам не надо слишком много теории, для этого есть куча технической документации), посмотрим для начала блок-схему работы модуля MSSP в режиме I2C

Сигналы с тактовыми импульсами и данными с контактов SDA и SDL приходят в модуль определения команды СТАРТ или СТОП, если какое-то условие из двух определилось, то выставится определённый бит в регистре SSPSTAT. Данная возможность актуальна при работе модуля в режиме ведомого I2C.

Если мы данные принимаем, то они с контакта SDA также поступают в регистр SSPSR побитно, а затем, когда байт загрузится полностью, он из этого регистра передастся в регистр SSPBUF, с которого мы его и считываем. Также данные из регистра поступают в регистр сравнения, в котором сравниваются с данными адресного регистра, в котором хранится адрес устройства, если мы также работаем с шиной в качестве ведомого устройства.

Теперь давайте немного поговорим о регистрах модуля MSSP. Хоть мы их уже и изучали, но изучали не все, а только те, которые принимают участие в обеспечении режима SPI, да и в тех регистрах, которые изучали, мы изучили также только те биты, которые также принимают участие в обеспечении режима SPI. Поэтому теперь мы изучим наши регистры применительно к режиму I2C.

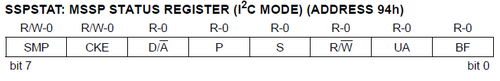

Начнём с регистра SSPSTAT и рассмотрим назначение его отдельных битов

бит 7: SMP (Slew Rate Control bit) — бит управления скоростью потока

Ведущий или ведомый режим I2C:

1 — управление длительностью фрона выключено в стандартном режиме (100 кГц и 1 МГц)

0 — управление длительность фронта включено в скоростном режиме (400 кГц)

бит 6: CKE (SPI Clock Select bit) — Выбор фронта передачи сигнала

Ведущий или ведомый режим I2C:

1 — Входные данные соответствуют спецификации SMBus

0 — Входные данные не соответствуют спецификации SMBus (соответствуют спецификации I2C).

бит 5 — D/A (Data/Address bit) — бит данных/адреса

Ведущий режим I2C: зарезервировано

Ведомый режим I2C

1 — последний считанный или переданный байт является информационным

0 — последний считанный или переданный байт не является информационным

бит 4 — P (Stop bit) — бит Stop

1 — бит STOP был обнаружен последним

0 — последним был не бит STOP

(данный бит сбрасывается после сброса бита SSPEN)

бит 3 — S (Start bit) — бит Start

1 — бит START был обнаружен последним

0 — последним был не бит START

(данный бит сбрасывается после сброса бита SSPEN)

бит 2 — R/W (Read/Write bit information) —

В режиме ведомого I2C:

1 — чтение

0 — запись

В режиме ведущего I2C:

1 — идёт процесс передачи данных

0 — передачи данных в данный момент не происходит

бит 1 — UA (Update Address bit) — флаг обновления адреса устройства

Используется только в режиме 10-разрядного адреса I2C в режиме ведомого устройства

1 — свидетельствует о необходимости обновления адреса в регистре SSPADD

0 — обновлять адрес в регистре не нужно

бит 0 — BF (Buffer Full Status bit) — флаг заполнения буфера

Для режима приёма:

1 — Приём закончен, SSPBUF полон

0 — Приём не закончен, SSPBUF пуст

Для режима передачи:

1 — Передача закончена (не включая бит ACK и бит STOP), SSPBUF полон

0 — Передача не закончена (не включая бит ACK и бит STOP), SSPBUF пуст

Следующий регистр управления — SSPCON1

бит 7 — WCOL (Write Collision Detect bit) — флаг обнаружения коллизии

В режиме ведущего устройства — передача

1 — Была предпринята попытка запись в регистр SSPBUF при несоблюдении условий шины I2C для начала передачи (должен быть очищен программно).

0 — Нет коллизии.

В режиме ведомого устройства — передача

1 — Была предпринята попытка запись в регистр SSPBUF в момент передачи предыдущего байта (слова) (должен быть очищен программно).

0 — Нет коллизии.

В режиме приёма данный бит ни на что не влияет.

бит 6 — SSPOV (Receive Overflow Indicator bit) — флаг переполнения

В режиме приёма

1 — Принят байт в тот момент, когда регистр SSPBUF содержал предыдущие данные, поэтому регистр SSPSR потеряет байт (должен быть очищен программно).

0 — Нет переполнения.

Значение бита не важно при передаче данных

бит 5 — SSPEN (Synchronous Serial Port Enable bit) — включение модуля MSSP

1 — MSSP включен и ножки SDA и SCL сконфигурированы как ножки SSP.

0 — MSSP отключен и ножки сконфигурированы как ножки I/O

При включении ножки должны быть настроены для работы в правильном направлении при помощи регистра TRISxx.

бит 4 — CKP (Release Control bit) — бит управления тактирования

В режиме ведомого устройства

1 — не управлять тактовым сигналом

0 — удерживаем ножку в низком уровне (используется для подготовки данных)

В режиме ведущего устройства значение данного бита не важно

биты 3-0 — SSPM3:SSPM0 (Synchronous Serial Port Mode Select bits) — биты выбора режима работы модуля MSSP

1111 — Ведомый режим I2C, 10-битная адресация с разрешением прерывания при приёме команд START и STOP

1110 — Ведомый режим I2C, 7-битная адресация с разрешением прерывания при приёме команд START и STOP

1011 — Программная поддержка ведущего режима I2C (ведущий режим выключен)

1000 — Ведущий режим I2C, частота — FOSC/(4 * (SSPADD + 1))

0111 — Ведомый режим I2С, 10-битная адресация

0110 — Ведомый режим I2С, 7-битная адресация

Для режима SPI комбинации битов здесь не указаны.

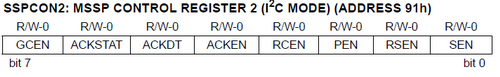

Есть ещё один управляющий регистр — SSPCON2

бит 7 — GCEN (General Call Enable bit ) — бит разрешения поддержки общего вызова

В режиме ведомого устройства

1 — Разрешение прерываний при приёме в регистр SSPSR (0000h)

0 — Поддержка общего вызова выключена

В режиме ведущего не используется

бит 6 — ACKSTAT (Acknowledge Status bit) — бит статуса подтверждения

В режиме ведущего устройства

1 — Подтверждение от ведомого не получено

0 — Подтверждение от ведомого получено

В режиме ведомого не используется

бит 5 — ACKDT (Acknowledge Data bit) — бит подтверждения

В режиме приёма ведущего устройства

1 — Подтверждение

0 — Нет подтверждения

В режиме ведомого, а также в режиме передачи ведущего устройства не используется

бит 4 — ACKEN (Acknowledge Sequence Enable bit) — бит формирования бита подтверждения

В режиме приёма ведущего устройства

1 — На выводах SCL и SDA формируется бит ACKDT. Автоматически сбрасывается аппаратно

0 — Подтверждение не формируется

В режиме ведомого, а также в режиме передачи ведущего устройства не используется

бит 3 — RCEN (Receive Enable bit) — бит разрешения приёма данных

В режиме приёма ведущего устройства

1 — Включить режим приёма I2C

0 — Приём отключен

В режиме ведомого, а также в режиме передачи ведущего устройства не используется

бит 2 — PEN (Stop Condition Enable bit) — бит формирования бита STOP

В режиме ведущего устройства

1 — На выводах SCL и SDA формируется бит STOP. Автоматически сбрасывается аппаратно

0 — Формирование бита STOP отключено

В режиме ведомого устройства не используется

бит 1 — RSEN (Repeated Start Condition Enabled bit) — бит формирования повторного бита START

В режиме ведущего устройства

1 — На выводах SCL и SDA формируется повторный бит START. Автоматически сбрасывается аппаратно

0 — Повторный START отключен

В режиме ведомого устройства не используется

бит 0 — SEN (Start Condition Enabled/Stretch Enabled bit) — формирование бита START

В режиме ведущего устройства

1 — На выводах SCL и SDA формируется бит START. Автоматически сбрасывается аппаратно

0 — START не формируется

В режиме ведущего устройства

1 — Длительное растяжение включено (и для передачи, и для приёма). Возможность растягивания

0 — Длительное растяжение включено (только для передачи). Поддерживается только в контроллерах PIC16F87x

Ну, вроде с регистрами всё. Думаю, регистр адреса рассматривать не будем. Там просто биты значения.

Всё остальное будем изучать при необходимости во время написания кода, так как всё описать невозможно (режим конкуренции, арбитраж и т.д.). Да и устали уже от теории.

В следующей части урока мы познакомимся с микросхемой памяти EEPROM AT24C32D, настроим наш проект и напишем ряд служебных функций.

Предыдущий урок Программирование МК PIC Следующая часть

Купить программатор (неоригинальный) можно здесь: PICKit3

Купить программатор (оригинальный) можно здесь: PICKit3 original

Отладочную плату PIC Open18F4520-16F877A можно приобрести здесь: PIC Open18F4520-16F877A

Модуль RTC DS3231 с микросхемой памяти (3 шт)

Модуль RTC DS3231 с микросхемой памяти (1 шт) — так дороже

Индикатор 4-разрядный LED WaveShare можно приобрести здесь: LED WaveShare

Логический анализатор 16 каналов можно приобрести здесь

Смотреть ВИДЕОУРОК (нажмите на картинку)

Добавить комментарий