Продолжаем знакомство с библиотекой LL (low-layer drivers).

На прошлом занятии мы узнали о преимуществах данной библиотеки, поработали с ножками порта, а теперь давайте попробуем поработать с таймерами.

С таймерами, вообще-то, мы работаем уже давно и постоянно, но с использованием библиотеки LL мы с ними пока не общались.

Что такое таймеры, для чего они нужны и первоначальное знакомство с ними было в уроке 5, но с использованием библиотеки HAL. Также в этом уроке контроллер был другой — из серии F4. У серии контроллеров F1 таймеры приблизительно те же, но есть и некоторые отличия. Также в 5 уроке мы знакомились с таймерами не совсем подробно, мы даже не изучили, какие регистры существуют для работы с таймерами и для чего они нужны.

В данном уроке мы также не будет полностью изучать все регистры таймеров, так как их очень много, а использовать мы их будем пока не все. Поэтому познакомимся мы лишь с теми, которые будут задействованы в данном занятии, чтобы не забивать пока голову лишней информацией.

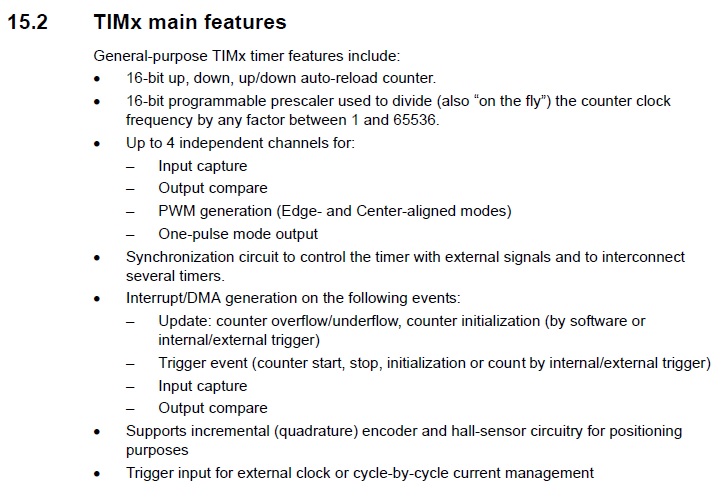

Пока давайте познакомимся, какие вообще есть таймеры у контроллеров серии STM32F1.

Открываем reference manual и перейдём в главу 14 — Advanced-control timers (TIM1&TIM8).

Эти два таймера — таймеры с расширенным управлением.

Данные таймеры 16-битные и выполнять они могут следующие функции:

- захват входного значения,

- выдача сигнала по сравнению,

- генерирование ШИМ (PWM),

- режим генерации одного импульса.

Следующая линейка таймеров — таймеры со 2 до 5-го (глава 15).

Данные таймеры также 16-битные в отличие от серии F4, но функционал у них также очень широк

Таймеры 9-14 — тоже 16-битные, функционал подобен остальным.

Таймеры 6 и 7 — базовые, считают только вверх, но могут использоваться для активации ЦАП (DAC).

Также таймеры могут ещё много чего, но в данном занятии мы это не используем. Использовать мы будем только восходящий счётчик, его переполнение, следить за которым будем в обработчике прерывания.

Теперь познакомимся с некоторыми регистрами таймера, хотя напрямую библиотека LL с регистрами не работает, но уже очень близка к ним, так как хоть и нет в именах функций явного указания регистров и их битов, но порой некоторые их названия или часть названий в именах функций прослеживаются. Также о регистрах полезно знать для общего развития, а также для будущего использования возможностей библиотеки CMSIS.

Таймер мы будем использовать второй, поэтому и регистры будем брать из линейки таймеров, в которые входит данный таймер.

Начнём с первого регистра — управляющего регистра CR1

Рассмотрим отдельные биты данного регистра:

Биты 9:8: CKD (Clock division) — настройки делителя

00: tDTS = tCK_INT

01: tDTS = 2 * tCK_INT

10: tDTS = 4 * tCK_INT

11: Зарезервировано.

CK_INT — частота тактирования таймера, соответственно, tCK_INT — время (или период) одного такта.

Бит 7: ARPE (Auto-reload preload enable) — бит включения предзагрузки регистра

0 — у регистра TIMx_ARR буферизация отключена,

1 — у регистра TIMx_ARR буферизация включена.

Биты 6:5: CMS (Center-aligned mode selection) — выбор режима с выравниванием по краю или одного из режимов с выравниванием по центру

00: режим с выравниванием по краю; счёт ведётся вверх или вниз (режим суммирующего или вычитающего счётчика) в зависимости от значения бита направления DIR,

01: режим 1 с выравниванием по центру; счёт ведётся вверх и вниз поочерёдно; но при счёте вниз происходит установка флага прерывания сравнения для каналов, которые сконфигурированы как выходы (CCxS=00 в регистре TIMx_CCMRx),

10: режим 2 с выравниванием по центру; счёт ведётся вверх и вниз поочерёдно; но при счёте вверх происходит установка флага прерывания сравнения для каналов, которые сконфигурированы как выходы (CCxS=00 в регистре TIMx_CCMRx),

11: режим 3 с выравниванием по центру; счёт ведётся вверх и вниз поочерёдно; установка флага прерывания сравнения для каналов, которые сконфигурированы как выходы (CCxS=00 в регистре TIMx_CCMRx) происходит как при счёте вверх, так и при счёте вниз.

Бит 4: DIR (Direction) — бит направления счёта

0: счёт вверх

1: счёт вниз

Бит 3: OPM (One-pulse mode) — бит режима одиночного импульса

0: при возникновении события обновления счётчик не останавливается

1: при возникновении события обновления счётчик останавливается

Бит 2: URS (Update request source) — бит источника запроса на обновление

0: к генерации прерывания обновления или запроса DMA (если разрешено) привело любое из следующих событий:

— переполнение/антипереполнение счётчика;

— установка бита UG;

— обновление, генерируемое с помощью контроллера подчинённого режима.

1: только переполнение (или обнуление при обратном счёте) привело к генерации UEV

Бит 1: UDIS (Update disable) — данный бит устанавливается и очищается программно для разрешения/запрета генерации события обновления (UEV)

0: разрешена генерация UEV; случаи, в которых генерируется UEV, определяются значением бита URS

1: генерация UEV отключена, теневые регистры сохраняют свои значения неизменными (ARR, PSC, CCRx), но счётчик и предделитель сбрасываются при установке бита UG или при получении сигнала аппаратного сброса от контроллера подчинённого режима.

Бит 0: CEN (Counter enable) — бит включения счётчика

0: счётчик выключен

1: счётчик включен

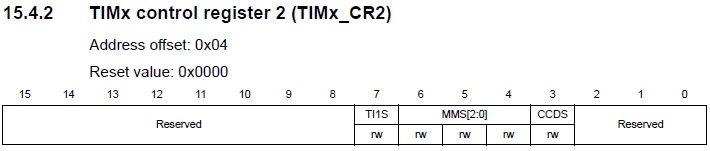

Следующий — управляющего регистра CR2

Назначение конкретных битов регистра:

Бит 7: TI1S (TI1 selection) — бит выбора входа TI1

0: к входу TI1 подключается вывод TIMy_CH1 микроконтроллера

1: на вход TI1 подаётся XOR (исключающее ИЛИ) от сигналов с выводов TIMx_CH1, CH2 и CH3 (TI1=CH1 xor CH2 xor CH3).

Биты 6:4: MMS2:MMS0 (Master mode selection) — выбор мастер-режима (при совместном использовании нескольких таймеров)

Возожны следющие варианты:

000: Reset — сброс, в качестве сигнала TRGO используется бит UG регистра TIMx_EGR. Если сброс выполняется входным триггерным сигналом (контроллер подчинённого режима сконфигурирован в режиме перезагрузки), то сигнал TRGO задерживается относительно действительного момента сброса

001: Enable — включение, в качестве сигнала TRGO используется сигнал запуска счёта CNT_EN. Режим может использоваться, например, для одновременного запуска нескольких таймеров или для управления окном, на протяжении которого включён подчинённый таймер. Сигнал CNT_EN является результатом логической операции OR (ИЛИ) между управляющим битом CEN и входным триггерным сигналом при работе таймера в стробирующем режиме (gated mode). Если сигнал CNT_EN управляется входным триггерным сигналом, тогда TRGO формируется с задержкой, за исключением случая, когда выбран режим master/slave (смотрите описание бита MSM регистра TIMx_SMCR)

010: Update — событие обновления формирует сигнал TRGO. Это, например, позволяет использовать таймер в качестве предделителя для подчинённого таймера (таким образом могут быть сформированы весьма продолжительные интервалы времени)

011: Compare Pulse — импульс TRGO формируется тогда, когда устанавливается флаг CC1IF (даже если он уже содержал значение 1), это происходит при входной фиксации или при срабатывании схемы сравнения

100: Compare — сигнал OC1REF используется в качестве TRGO

101: Compare — сигнал OC2REF используется в качестве TRGO

110: Compare — сигнал OC3REF используется в качестве TRGO

111: Compare — сигнал OC4REF используется в качестве TRGO.

Бит 3: CCDS (Capture/compare DMA selection) — бит определяет, в каких случаях формируется запрос DMA

0: CCx запрос DMA формируется, когда происходит событие CCx

1: CCx запрос DMA формируется, когда происходит событие обновления.

Следующий — регистр состояния SR

Биты регистра:

Биты 12:9: CC4OF:CC1OF (Capture/Compare 4…1 overcapture flag) — биты переполнения флага входной фиксации (при работе канала в режиме входа), устанавливаются аппаратно в случае, если происходит фиксация значения счётчика в данном канале (фиксируемое значение помещается в регистр TIMx_CCRy, y=1..4) и при этом флаг фиксации CCyIF у этого канала уже установлен. Сброс бита выполняется программно путём записи в него значения 0.

0: переполнения флага не происходило

1: обнаружено переполнение флага.

Бит 6: TIF (Trigger interrupt flag) — данный флаг устанавливается аппаратно триггерным событием (trigger event), которое возникает под действием активного фронта сигнала на входе TRGI при включенном контроллере подчинённого режима во всех режимах, кроме стробирующего. Сбрасывается программно.

0: событие не происходило

1: обнаружено триггерное событие.

Биты 4:1: CC4IF (Capture/Compare 4…1 interrupt flag) — назначение данных битов зависит от режима работы канала. Сбрасывается программно.

При работе в режиме сравнения, когда канал используется для формирования выходного сигнала

0: совпадение не происходило

1: установка бита происходит при обнаружении равенства содержимого счётчика и содержимого регистра TIMx_CCRy в данном канале; в случае, если TIMx_CCRy превышает значение в регистре перезагрузки TIMx_ARR (а значит, счётчик никогда не достигнет значения в регистре сравнения), то бит устанавливается в 1 при переполнении счётчика (в режимах счёта вверх и вверх/вниз) или обнуления (в режиме счёта вниз).

Бит 0: UIF (Update interrupt flag) — данный флаг устанавливается при возникновении события обновления. Устанавливается аппаратно, сбрасывается программно

0: событие обновления не происходило

1: обнаружено событие обновления.

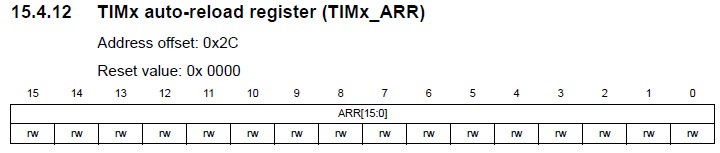

Следующий — регистр автоматической перезагрузки ARR

В 16 битах данного регистра содержится число для автоматической перезагрузки счётчика. Сюда мы заносим число, до которого будет считать счётчик. Как только досчитает, перезагрузится и начнёт счёт с нуля.

Следующий — регистр предделителя PSC

Биты данного числа содержат значение коэффициента деления предделителя.

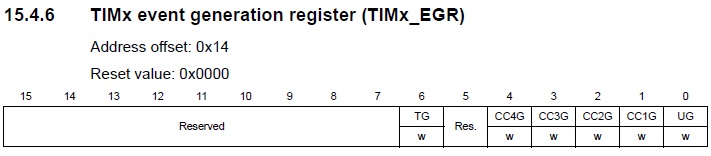

Следующий — регистр генерации событий EGR

Биты данного регистра работают только на запись.

Назначение их следующее:

Бит 6: TG (Trigger generation) — бит генерации триггерных событий, устанавливается программно

0: событие не генерируется

1: генерация триггерного события, устанавливается флаг TIF в регистре TIMx_SR; возможна генерация прерывания и запроса DMA (если разрешено)

Бит 4:1: CC4G, CC3G, CC2G, CC1G (Capture/compare 4-1 generation) — биты генерации событий фиксации / сравнения. Эти биты устанавливается программно для генерации события фиксации/сравнения (Capture/Compare) для соответствующего канала таймера (1, 2, 3, 4), а сброс бита происходит аппаратно.

0: событие не генерируется

1: генерация события Capture/Compare в соответствующем канале таймера (1, 2, 3, 4), действие бита зависит от режима работы канала

Бит 0: UG (Update generation) — бит генерации события обновления. Данный бит устанавливается программно, сбрасывается аппаратно.

0: событие не генерируется

1: генерация события обновления. происходит инициализация счётчика и обновляется содержимое буферизируемых регистров, а также сбрасывается счётчик предделителя (коэффициент деления не изменяется). В режиме с выравниванием по центру, счётчик таймера сбрасывается в 0 при DIR=0 (во время счёта вверх) и инициализируется значением из регистра TIMx_ARR при DIR=1 (счёт вниз).

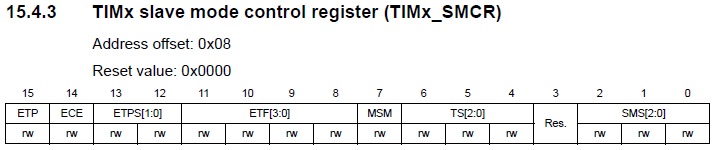

Следующий — регистр управления подчинённым режимом таймера SMCR

Назначение битов данного регистра следующее:

Бит 15: ETP (External trigger polarity) — бит выбора сигнала, используемого как триггерный (ETR или его инверсия — not ETR).

0: ETR не инвертируется, активным является высокий уровень или нарастающий фронт

1: ETR инвертируется, активным является низкий уровень или спад сигнала.

Бит 14: ECE (External clock enable) — бит включения второго режима внешнего тактового сигнала

0: второй режим внешнего тактового сигнала отключен

1: второй режим внешнего тактового сигнала включён; счётчик тактируется каждым активным фронтом сигнала ETRF.

Биты 13:12: ETPS (External trigger prescaler) — биты настройки предделителя внешнего триггерного сигнала

00..11: коэффициент деления предделителя, который, соответственно, равен 1, 2, 4, 8.

Биты 11:8: ETF3:ЕTF0 (External trigger filter) — битовое поле настройки частоты сэмплирования сигнала ETRP и длины цифрового фильтра, применяемого к сигналу ETRP. Цифровой фильтр выполнен в виде счётчика событий и для подтверждения перехода сигнала требуется N последовательных событий считывания нового значения:

0000: фильтр не используется, частота сэмплирования равна fDTS;

0001: fSAMPLING=fCK_INT, N=2

0010: fSAMPLING=fCK_INT, N=4

0011: fSAMPLING=fCK_INT, N=8

0100: fSAMPLING=fDTS/2, N=6

0101: fSAMPLING=fDTS/2, N=8

0110: fSAMPLING=fDTS/4, N=6

0111: fSAMPLING=fDTS/4, N=8

1000: fSAMPLING=fDTS/8, N=6

1001: fSAMPLING=fDTS/8, N=8

1010: fSAMPLING=fDTS/16, N=5

1011: fSAMPLING=fDTS/16, N=6

1100: fSAMPLING=fDTS/16, N=8

1101: fSAMPLING=fDTS/32, N=5

1110: fSAMPLING=fDTS/32, N=6

1111: fSAMPLING=fDTS/32, N=8.

Бит 7: MSM (Master/Slave mode) — бит включения режима Master/Slave

0: режим отключен

1: режим включён. Вводится задержка между сигналом запуска на входе TRGI и его воздействием на таймер для достижения точной синхронизации между данным таймером и его подчинёнными таймерами (которые управляются сигналом TRGO, см. описание битового поля MMS в регистре TIMx_CR2). Этот режим может быть полезен, если требуется синхронизация нескольких таймеров одним внешним событием.

Биты 6:4: TS (Trigger selection) — поле выбора входного триггерного сигнала для синхронизации счётчика

000: Internal Trigger 0 (ITR0) — внутренний триггерный сигнал 0

001: Internal Trigger 1 (ITR1) — внутренний триггерный сигнал 1

010: Internal Trigger 2 (ITR2) — внутренний триггерный сигнал 2

011: Internal Trigger 3 (ITR3) — внутренний триггерный сигнал 3

100: TI1 Edge Detector (TI1F_ED) — детектор фронта сигнала TI1

101: Filtered Timer Input 1 (TI1FP1) — сигнал TI1 (после цифрового фильтра)

110: Filtered Timer Input 2 (TI2FP2) — сигнал TI2 (после цифрового фильтра)

111: External Trigger input (ETRF) — внешний триггерный вход ETRF.

Биты 2:0: SMS (Slave mode selection) — поле выбора типа подчинённого режима

000: подчинённый режим отключён; в этом случае при CEN=1 на предделитель поступает внутренний тактовый сигнал

001: режим 1 энкодера — счёт вверх/вниз по фронту на TI2FP1; направление счёта определяется уровнем сигнала TI1FP2

010: режим 2 энкодера — счёт вверх/вниз по фронту на TI1FP2; направление счёта определяется уровнем сигнала TI2FP1

011: режим 3 энкодера — счёт вверх/вниз по фронту на любом из двух входов TI1FP1, TI2FP2; направление счёта при прохождении импульса на одном входе определяется уровнем сигнала в этот момент на другом входе

100: Reset Mode, режим сброса — нарастающий фронт сигнала на выбранном триггерном входе (TRGI) сбрасывает счётчик и обновляет регистры

101: Gated Mode, стробирующий режим — таймер выполняет счёт при высоком уровне сигнала на триггерном входе (TRGI); счётчик останавливается (но не сбрасывается) при переходе сигнала на запускающем входе к низкому уровню; таким образом, внешний сигнал управляет как запуском, так и остановкой счётчика

110: Trigger Mode, триггерный режим — счётчик запускается (но не сбрасывается) нарастающим фронтом сигнала на триггерном входе TRGI; в отличие от стробирующего режима (Gated Mode), контролируется только запуск счётчика

111: External Clock Mode 1, режим 1 внешнего тактового сигнала — счётчик тактируется нарастающими фронтами на выбранном триггерном входе (TRGI).

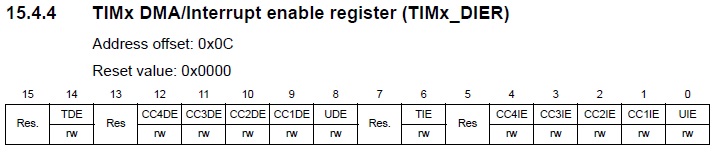

Следующий — регистр разрешения запросов DMA и прерываний DIER

Назначение отдельных битов регистра:

Бит 14: TDE (Trigger DMA request enable) — бит запрета/разрешения запросов DMA в ответ на триггерный сигнал

0: генерация запроса запрещена

1: генерация запроса разрешена

Бит 12: CC4DE (Capture/Compare 4 DMA request enable) — бит разрешения запрос DMA в случае выполнения входной фиксации или срабатывания схемы сравнения в канале 4.

0: Запрос CC4 DMA запрещен

1: Запрос CC4 DMA разрешен.

Бит 11: CC4DE (Capture/Compare 3 DMA request enable) — бит разрешения запрос DMA в случае выполнения входной фиксации или срабатывания схемы сравнения в канале 3.

0: Запрос CC3 DMA запрещен

1: Запрос CC3 DMA разрешен.

Бит 10: CC4DE (Capture/Compare 2 DMA request enable) — бит разрешения запрос DMA в случае выполнения входной фиксации или срабатывания схемы сравнения в канале 2.

0: Запрос CC2 DMA запрещен

1: Запрос CC2 DMA разрешен.

Бит 9: CC4DE (Capture/Compare 1 DMA request enable) — бит разрешения запрос DMA в случае выполнения входной фиксации или срабатывания схемы сравнения в канале 1.

0: Запрос CC1 DMA запрещен

1: Запрос CC1 DMA разрешен.

Бит 8: UDE (Update DMA request enable) — бит разрешения запроса DMA в случае события обновления

0: Запрос обновления DMA запрещен

1: Запрос обновления DMA разрешен.

Бит 6: TIE (Trigger interrupt enable) — бит разрешения прерывания в ответ на триггерный сигнал

0: Прерывание запрещено

1: Прерывание разрешено.

Бит 4: CC4IE (Capture/Compare 4 interrupt enable) — бит разрешения прерывания в случае выполнения входной фиксации или срабатывания схемы сравнения в канале 4

0: Прерывание запрещено

1: Прерывание разрешено.

Бит 3 CC3IE (Capture/Compare 4 interrupt enable) — бит разрешения прерывания в случае выполнения входной фиксации или срабатывания схемы сравнения в канале 3

0: Прерывание запрещено

1: Прерывание разрешено.

Бит 2: CC2IE (Capture/Compare 4 interrupt enable) — бит разрешения прерывания в случае выполнения входной фиксации или срабатывания схемы сравнения в канале 2

0: Прерывание запрещено

1: Прерывание разрешено.

Бит 1: CC1IE (Capture/Compare 4 interrupt enable) — бит разрешения прерывания в случае выполнения входной фиксации или срабатывания схемы сравнения в канале 1

0: Прерывание запрещено

1: Прерывание разрешено.

Бит 0: UIE (Update interrupt enable) — бит разрешения прерывания в случае, когда происходит событие обновления.

0: Прерывание запрещено

1: Прерывание разрешено.

В следующей части нашего урока мы создадим проект, чтобы полученные знания по таймерам закрепить на практике.

Предыдущий урок Программирование МК STM32 Следующая часть

Отладочную плату STM32F103C8T6 можно приобрести здесь STM32F103C8T6

Программатор недорогой можно купить здесь ST-Link V2

Смотреть ВИДЕОУРОК (нажмите на картинку)

Добавить комментарий