Продолжая изучать возможности библиотеки LL, на данном уроке мы начнём освоение аппаратной реализации шины SPI (Serial peripheral interface) в контроллере STM32F1.

С данной шиной мы работаем постоянно, но реализация её с помощью функционала библиотеки LL нами ещё не рассматривалась. Поэтому изучать подробно работу шины SPI, её протокол, режимы её работы, мы не будем. Подробно работа шины и подключение устройств друг к другу с помощью неё описана вот в этом уроке по контроллерам AVR. Сегодня мы попробуем подключить по данной шине к контроллеру STM32 восьмиразрядный семисегментный индикатор, динамическая индикация которого реализована на микросхеме-драйвере MAX7219. Данная микросхема общается с контроллером именно по шине SPI. Мы неоднократно уже работали с данной микросхемой с использованием других контроллеров: в уроке 28 мы подключали её к микроконтроллеру семейства AVR, в уроке 16 — к микроконтроллеру PIC. К контроллеру STM32 мы её также неоднократно подключали, в частности в уроке 26. Только до сих пор мы для работы с данной микросхемой по шине SPI использовали возможности библиотеки HAL. Теперь же попробуем реализовать отправку данных для индикации этой микросхеме с помощью функционала библиотеки LL.

И, как уже сложилось, сначала мы откроем техническую документацию на контроллер STM32F1xx и изучим несколько поподробнее, как реализована шина SPI в данном контроллере и какие регистры участвуют в её аппаратной реализации. Регистры шины SPI в нашем проекте будут использованы не все, вернее те, которые отвечают за реализации собственно шины SPI будут использованы все и мы их изучим, но модуль SPI в контроллере STM32 также умеет работать и с аудиошиной I2S и есть некоторые регистры, отвечающие именно за работу с шиной I2S. Вот именно эти регистры мы изучать и рассматривать в рамках данного занятия не будем.

Вот так выглядит блок-схема модуля SPI в контроллере STM32F1

На данной схеме мы видим, каким образом реализована шина SPI. Для обмена данными существуют ножки MOSI и MISO, о назначении которых мы уже давно прекрасно знаем, также есть ножка синхронизации SCK, подключенная к генератору импульсов синхронизации и также существует ножка выбора устройства NSS (мы привыкли называть её Chip Select). Данная ножка может быть задействована аппаратно, а может и программно, то есть она посредством определённых настроек может быть отключена. Обмен данными с подключенным устройством осуществляется через сдвиговый регистр, для отправки данные в него помещаются из буфера передачи, а пришедшие данные помещаются в буфер приёма. С данными буферами соединён регистр данных DR. Если мы данный регистр читаем, то мы читаем буфер приёма, а если мы в него пишем, то данные помещаются в буфер передачи. Настройки шины осуществляются посредством настройки битов управляющих регистров CR1 и CR2, а мониторинг работы ведётся с помощью отслеживания определённых битов регистра состояния SR1.

Теперь давайте перейдём непосредственно к изучению регистров.

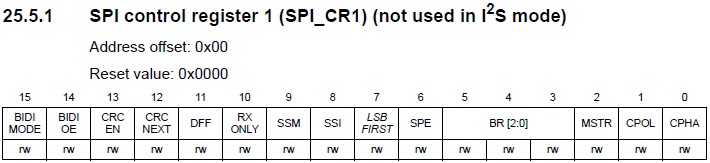

Первый регистр управления

Рассмотрим биты и битовые поля данного регистра подробно.

BIDIMODE (Bidirectional data mode enable): бит режима двунаправленного режима обмена

0 — обмен осуществляется по двум направлениям раздельно по разным линиям

1 — обмен осуществляется по двум направлениям по одной линии.

BIDIOE (Output enable in bidirectional mode): бит настройки однопроводного режима обмена данными

0 — данные только передаются

1 — данные только принимаются.

CRCEN (Hardware CRC calculation enable): бит включения аппаратного подсчёта контрольной суммы

0 — аппаратный подсчёт CRC отключен

1 — аппаратный подсчёт CRC включен.

CRCNEXT (CRC transfer next): бит включения передачи контрольной суммы в следующем кадре

0 — передачи контрольной суммы в следующем кадре нет

1 — следующий кадр — передача CRC.

DFF (Data frame format): Формат кадра

0 — передача данных в 8-битном формате

1 — передача данных в 16-битном формате.

RXONLY (Receive only): Бит управления направлением передачи данных в двухпроводном режиме

0 — разрешена и передача и приём данных (полный дуплекс)

1 — разрешен только приём данных.

SSM (Software slave management): бит управления ножкой выбора микросхемы в ведомом режиме (NSS)

0 — Состояние ножки контролируется в аппаратном режиме

1 — Состояние ножки не контролируется, контроль идёт по состоянию бита SSI.

SSI (Internal slave select): состояние данного бита заменяет состояние ножки NSS. Актуален только при установленном бите SSM. Значение этого бита подается на вывод NSS, а значение на выводе NSS игнорируется.

LSBFIRST (Frame format): бит очерёдности битов в кадре

0 — обмен данными производится старшим битом вперёд

1 — обмен производится старшим битом вперёд.

SPE (SPI enable): бит включения модуля

0 — модуль SPI отключен

1 — модуль SPI включен.

BR[2:0] (Baud rate control): битовое поле настройки скорости работы шины. В зависимости от комбинации значений битов данного поля устанавливается определённый делитель частоты работы шины, к которой подключен модуль (APB1)

000: fPCLK/2

001: fPCLK/4

010: fPCLK/8

011: fPCLK/16

100: fPCLK/32

101: fPCLK/64

110: fPCLK/128

111: fPCLK/256

MSTR (Master selection): Настройка типа устройства

0 — SLAVE.

1 — MASTER.

CPOL (Clock polarity): Настройка полярности шины синхронизации

0 — в режиме ожидания уровень низкий

1 — в режиме ожидания уровень высокий.

CPHA (Clock phase): Настройка фазы считывания значения бита

0 — выброка данных по переднему фронту сигнала CLK

1 — выброка данных по заднему фронту (по спаду) сигнала CLK.

Второй управляющий регистр

Назначение битов данного регистра:

TXEIE (Tx buffer empty interrupt enable): бит включения прерываний пустоты буфера передачи

0 — прерывания TXE запрещены

1 — прерывания TXE разрешены.

RXNEIE (RX buffer not empty interrupt enable): бит включения прерываний полноты (когда буфер не пуст) буфера приёма

0 — прерывания RXNEIE запрещены

1 — прерывания RXNEIE разрешены.

ERRIE (Error interrupt enable)): бит включения прерываний при возникновении ошибок

0 — прерывания при возникновении ошибок запрещены

1 — прерывания при возникновении ошибок разрешены.

SSOE (SS output enable): бит управления ножкой NSS в режиме MASTER

0 — управление ножкой в режиме MASTER отключено

1 — вывод NSS используется в качестве выхода и модуль SPI управляет данной ножкой сам. Из-за не совсем хорошего алгоритма управления мы чаще всего аппаратное управление данным выводом не используем, а используем программное.

TXDMAEN (Tx buffer DMA enable): флаг разрешения формирования запроса к DMA при установке бита TXE

0 — формирование запроса запрещено

1 — формирование запроса разрешено.

RXDMAEN (Rx buffer DMA enable): флаг разрешения формирования запроса к DMA при установке бита RXNE

0 — формирование запроса запрещено

1 — формирование запроса разрешено.

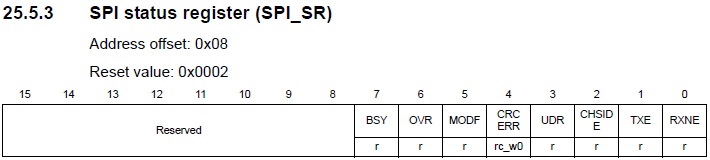

Следующий регистр состояния модуля

Назначение отдельных битов данного регистра:

BSY (Busy flag): флаг занятости шины

0 — шина свободна

1 — шина занята или буфер TX не пуст.

OVR (Overrun flag): флаг переполнения буфера

0 — переполнение буфера не обнаружено

1 — обнаружено переполнение буфера или новые данные в буфере пытаются перезаписать старые, которые ещё не были прочитаны.

MODF (Mode fault): Флаг обнаружения на шине NSS низкого уровня в режиме MASTER. Устанавливается аппаратно, сбрасывается только путём определённой последовательности

0 — обнаружения низкого уровня не зафиксировано

1 — обнаружен низкий уровень на шине NSS в режиме MASTER.

CRCERR (CRC error flag): флаг ошибки контрольной суммы

0 — ошибка контрольной суммы не обнаружена

1 — контрольная сумма отличается от рассчитанной.

UDR (Underrun flag): флаг недостаточного заполнения буфера. Актуален только для режима I2S. Также должен быть установлен бит ERRIE в регистре CR2. Устанавливается когда программа ещё не загрузила значение в регистр DR. Очищается чтением регистра SR.

0 — неполного заполнения буфера не обнаружено

1 — буфер заполнен не полностью.

CHSIDE (Channel side): флаг канала. Не актуален в режиме SPI

0 — левый канал должен быть передан или получен

1 — правый канал должен быть передан или получен.

TXE (Transmit buffer empty): флаг пустоты буфера передачи

0 — буфер не пуст, то есть данные из регистра DR при передаче ещё не переместились в сдвиговый регистр

1 — буфер пуст, то есть данные из регистра DR при передаче переместились в сдвиговый регистр.

RXNE (Receive buffer not empty): буфер заполнения буфера приёма

0 — буфер ещё не заполнен, то есть при приёме данные из сдвигового регистра ещё не поступили в регистр DR

1 — буфер заполнен, то есть при приёме данные из сдвигового регистра успешно и полностью поступили в регистр DR.

Следующий регистр — это регистр данных

В данный регистр из регистра сдвига поступают данные при приёме, из него мы их впоследствии и считываем, а также в этот регистр мы записываем данные для их дальнейшей передачи тому или иному устройству.

Ну вот мы и завершили знакомство с аппаратной организацией шины SPI в контроллере STM32F1.

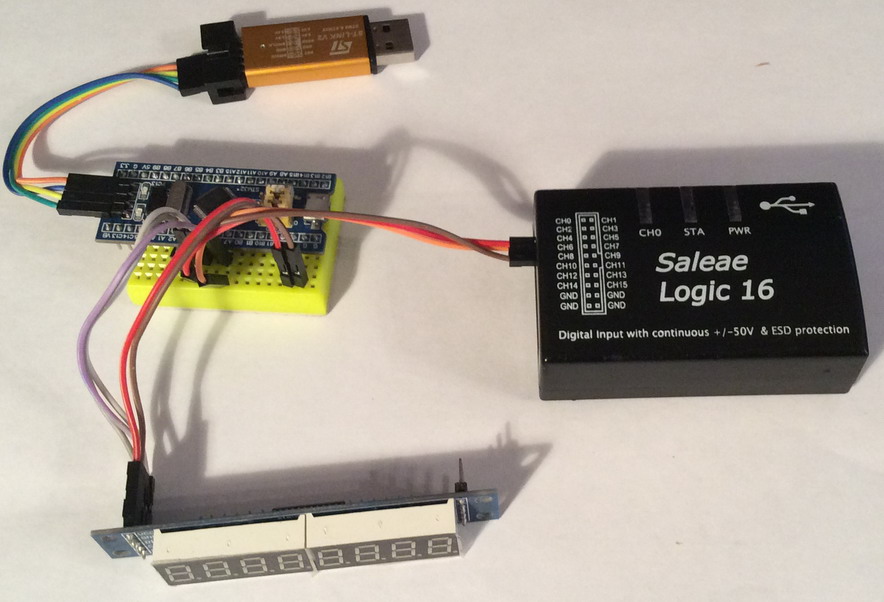

Теперь давайте познакомимся со схемой. Схема также простейшая. Питается плата индикатора с микросхемой от нашей платы с контроллером, поэтому пятью проводами к плате контроллера подключим индикатор к соответствующим ножкам. Также подключим к сигнальным ножкам MOSI, CLK и SS логический анализатор для наглядного контроля наших действий

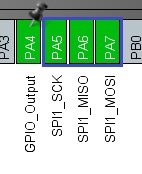

Теперь перейдём к проекту. Проект создадим из проекта урока 146 с именем LL_BLINK01 и назовём его LL_LED7219.

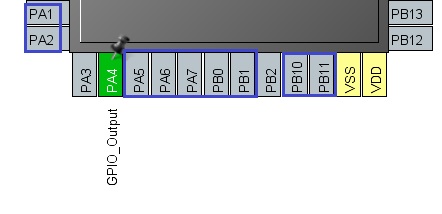

Откроем проект в Cube MX и сначала отключим все ножки портов, которые были у нас настроены и на вход и на выход, кроме одной — PA4. Эта ножка будет у нас ножкой SS для нашей шины SPI

Немного добавим скорости данной ножке

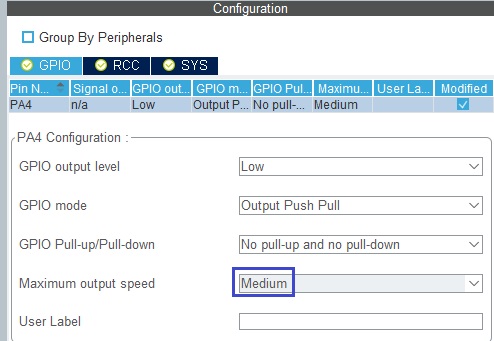

Включим шину SPI и настроим там делитель частоты

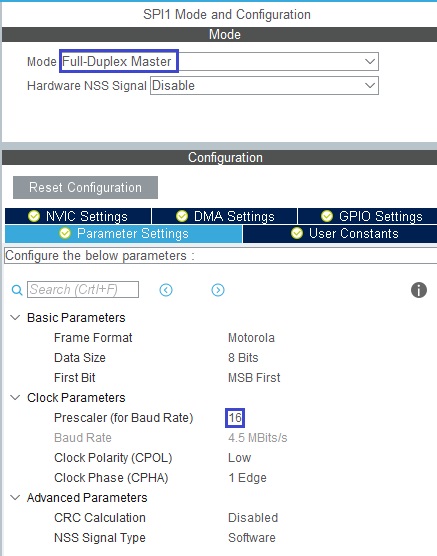

У нас включились следующие ножки, к ним мы и подключаем устройство

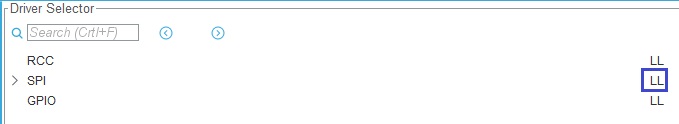

Также не забываем задействовать именно библиотеку LL для работы с шиной SPI

Сгенерируем проект, откроем его в Keil, настроим программатор на автоматическую перезагрузку и также уберём оптимизацию.

В следующей части занятия мы проследим, как происходит инициализация шины SPI в нашем проекте, напишем код для работы с индикатором, а также проверим работу кода на практике.

Предыдущий урок Программирование МК STM32 Следующая часть

Отладочную плату STM32F103C8T6 можно приобрести здесь STM32F103C8T6

Программатор недорогой можно купить здесь ST-Link V2

Индикатор светодиодный семиразрядный с драйвером MAX7219

Логический анализатор 16 каналов можно приобрести здесь

Смотреть ВИДЕОУРОК (нажмите на картинку)

Добавить комментарий