Продолжая изучать возможности библиотеки LL, на данном уроке мы начнём освоение аппаратной реализации шины USART (Universal synchronous asynchronous receiver transmitter) в контроллере STM32F1.

С данным интерфейсом мы работаем постоянно, но реализация его с помощью функционала библиотеки LL нами пока не рассматривалась. Поэтому изучать подробно работу шины USART, её протокол, режимы её работы, мы не будем. Подробно работа шины и подключение устройств друг к другу с помощью неё описана вот в этом уроке по контроллерам AVR.

Технические характеристики USART контроллере STM32F1 мы также рассматривать не будем, с ними мы будем постепенно знакомиться уже на этапе создания проектов, скажу лишь, что по сравнению с аналогичной шиной в контроллере AVR есть ряд отличий, в том числе в контроллере STM32 уже можно организовать аппаратное управление потоком с помощью специальных ножек RTS и CTS. Порой данные ножки используются ещё для некоторых целей. Но об этом в будущем.

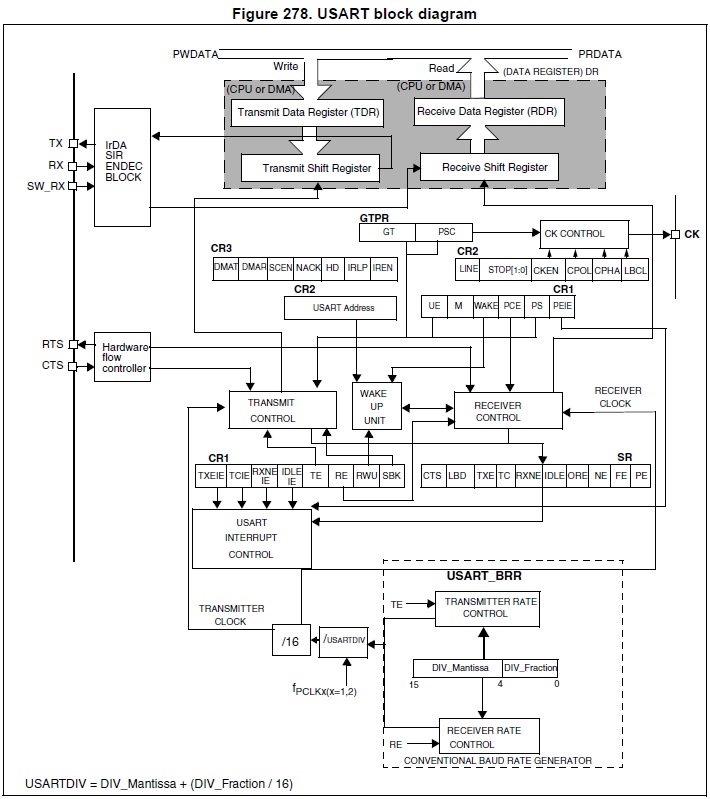

Посмотрим сначала блок-схему шины USART в нашем контроллере

Здесь мы видим, что имеются целых три управляющих регистра, регистр состояния, регистр данных, в который входят 2 регистра для передачи и 2 — для приёма, регистр времени защиты и предделителей (GTPR), . Также имеется в наличии блок управления скоростью потока (генератор бит-рейта), включающий в себя также и регистр управления скоростью потока, управляемый делитель частоты тактирования бит-рейт-генератора, контроллер управления аппаратным потоком и много чего ещё интересного.

Прежде чем начать работу с интерфейсом USART с применением библиотеки LL, мы сначала подробно изучим его регистры, все их биты и битовые поля, организованные в контроллере STM32F1.

По традиции начнём с регистров управления.

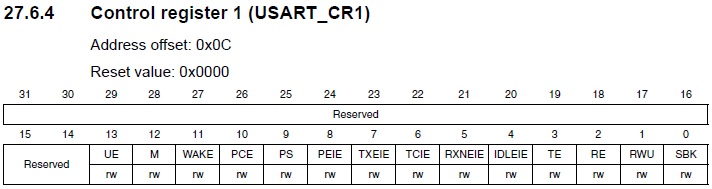

Первый рассматриваемый нами регистр — регистр управления 1 (control register 1)

Теперь поподробнее о битах данного регистра

UE (USART enable): бит разрешения работы USART

0 — шина выключена

1 — шина включена.

M (Word length): бит длины слова

0 — 8 бит данных

1 — 9 бит данных.

WAKE (Wakeup method): способ пробуждения

0 — по свободной линии

1 — по маркеру адреса.

PCE (Parity control enable): бит контроля чётности

0 — чётность не контролируется

1 — контроль чётности включен.

PS (Parity selection): тип контроля чётности

0 — проверка на чётность

1 — проверка на нечётность.

PEIE (PE interrupt enable): бит включения прерываний по чётности

0 — прерывания запрещены

1 — прерывания разрешены.

TXEIE (TXE interrupt enable): бит включения прерываний по опустошению буфера передатчика

0 — прерывания запрещены

1 — прерывания разрешены.

TCIE (Transmission complete interrupt enable): бит включения прерываний по окончанию передачи

0 — прерывания запрещены

1 — прерывания разрешены.

RXNEIE (RXNE interrupt enable): бит включения прерываний по заполнению буфера приёмника

0 — прерывания запрещены

1 — прерывания разрешены.

IDLEIE (IDLE interrupt enable): бит включения прерываний по окончанию приёма (освобождения линии)

0 — прерывания запрещены

1 — прерывания разрешены.

TE (Transmitter enable): бит включения передатчика

0 — передатчик выключен

1 — передатчик включен.

RE (Receiver enable): бит включения приёмника

0 — приёмник выключен

1 — приёмник включен.

RWU (Receiver wakeup): бит перевода приёмника в спящий режим

0 — режим активный

1 — режим спящий.

SBK (Send break): бит включения передачи символов BREAK. После передачи символа (вернее кода символа) бит очищается автоматически

0 — нет передачи Break

1 — передача Break.

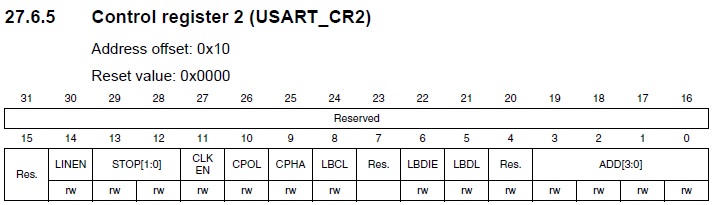

Следующий регистр — регистр управления 2 (control register 2)

Назначение битов регистра.

LINEN (LIN mode enable): бит включения режима LIN.

LIN (Local Interconnect Network) — это специальный стандарт промышленной сети, в котором также умеет работать наш USART.

0 — режим LIN не используется

1 — режим LIN включен.

STOP (STOP bits): битовое поле управления стоповыми битами

00 — 1 стоповый бит

01 — 0.5 стоповых бит

10 — 2 стоповых бита

11 — 1.5 стоповых бита

CLKEN (Clock enable): бит разрешения работы линии синхронизации (контакт CK)

0 — синхронизация не используется

1 — синхронизация включена.

CPOL (Clock polarity): бит полярности линии CK

0 — уровень готовности линии CK — низкий

1 — уровень готовности линии CK — высокий.

CPHA (Clock phase): бит фазы линии CK

0 — данные пойдут по фронту первого тактового импульса

1 — данные пойдут по фронту второго тактового импульса.

LBCL (Last bit clock pulse): данный бит позволяет выбрать, должен ли тактовый импульс, связанный с последним битом данных (MSB), выводиться на вывод CK в синхронном режиме

0 — последний бит не выводится на линию CK

1 — последний бит выводится на линию CK.

LBDIE (LIN break detection interrupt enable): разрешение прерываний от шины в режиме LIN по обнаружению прерывания (в буквальном смысле или перерыва) на линии

0 — прерывания запрещены

1 — прерывания разрешены.

LBDL (lin break detection length): бит длительности прерывания (перерыва) на линии в режиме LIN

0 — 10 бит

1 — 11 бит.

ADD[3:0] (Address of the USART node): битовое поле адреса на шине в для мультипроцессорной коммуникации.

Следующий регистр — регистр управления 3 (control register 3)

Назначение битов регистра:

CTSIE (CTS interrupt enable): разрешение прерывания от линии CTS

0 — прерывания запрещены

1 — прерывания разрешены.

CTSE (CTS enable): разрешение использования линии CTS

0 — линия не используется

1 — линия включена.

RTSE (RTS enable): разрешение использования линии RTS

0 — линия не используется

1 — линия включена.

DMAT (DMA enable transmitter): Включение DMA для передатчика

0 — DMA не используется

1 — DMA включен.

DMAR (DMA enable receiver): Включение DMA для приемника

0 — DMA не используется

1 — DMA включен.

SCEN (Smartcard mode enable): режим работы со смарткартами

0 — режим работы со смарткартами не используется

1 — режим работы со смарткартами включен.

NACK (Smartcard NACK enable): бит разрешения передачи условия NACK (нет подтверждения) в случае ошибки в режиме работы со смарткартами

0 — передача NACK не используется

1 — передача NACK включена.

HDSEL (Half-duplex selection): Включение полудуплексного режима (режим однопроводной передачи данных в оба направления

0 — полудуплексный режим не используется

1 — полудуплексный режим включен.

IRLP (IrDA low-power): бит выбора режима работы в режиме ИК

0 — обычный режим

1 — режим пониженного энергопотребления.

IREN (IrDA mode enable): бит включения режима ИК (передачи по инфракрасному порту)

0 — режим ИК не используется

1 — режим ИК включен.

EIE (Error interrupt enable): бит разрешения прерываний в случае ошибки. Генерация прерываний в случае ошибки кадрирования, ошибки переполнения или шумовой ошибки (флаги FE, ORE и NE)

0 — прерывания запрещены

1 — прерывания разрешены.

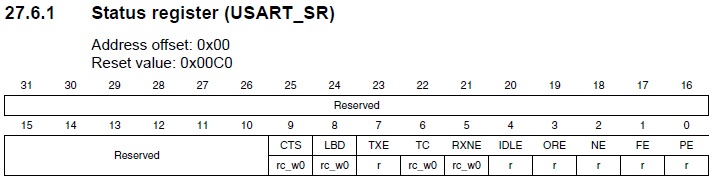

Следующий регистр — регистр состояния (Status register)

Назначение битов данного регистра:

CTS (CTS flag): бит обнаружения изменения уровня на линии CTS (если такая включена). Сбрасывается программно

0 — изменения состояния линии CTS не происходило

1 — произошло изменение состояния линии CTS.

LBD (LIN break detection flag) — флаг перерыва (прерывания) на шине LIN. Сбрасывается программно

0 — перерыва не происходило

1 — произошел перерыв (прерывание) на шине LIN.

TXE (Transmit data register empty): флаг опустошения буфера передатчика. Сбрасывается с помощью записи в регистр DR

0 — опустошения буфера передатчика не было

1 — произошло опустошение буфера передатчика.

TC (Transmission complete): флаг завершения передачи. Отличие от TXE в том, что не только буфер очищен, но ещё и сдвиговый регистр отработал. Сбрасывается программно записью 0 в данный бит.

0 — завершения передачи не происходило

1 — произошло завершение передачи.

RXNE (Read data register not empty): флаг заполнения буфера приёмника. Сбрасывается чтением регистра DR

0 — заполнения буфер приёмника не было

1 — произошло заполнение буфера приёмника.

IDLE (IDLE line detected): линия свободна. Сбрасывается чтением сначала регистра SR, потом DR

0 — линия занята

1 — линия свободна.

ORE (Overrun error): флаг переполнения буфера. Сбрасывается чтением сначала регистра SR, потом DR

0 — переполнение буфера не обнаружено

1 — обнаружено переполнение буфера или новые данные в буфере пытаются перезаписать старые, которые ещё не были прочитаны.

NE (Noise error flag): флаг обнаружения шума на линии. Сбрасывается чтением сначала регистра SR, потом DR

0 — шума не обнаружено

1 — обнаружен шум на линии.

FE (Framing error): флаг ошибки кадра. Сбрасывается чтением сначала регистра SR, потом DR

0 — ошибки кадра не обнаружено

1 — обнаружена ошибка кадра.

PE (Parity error): ошибка при проверке чётности, например, дважды пришёл нечётный кадр. Сбрасывается чтением сначала регистра SR, потом DR. Только перед чтением надо подождать, когда установится бит RXNE

0 — ошибки чётности не обнаружено

1 — обнаружена ошибка чётности.

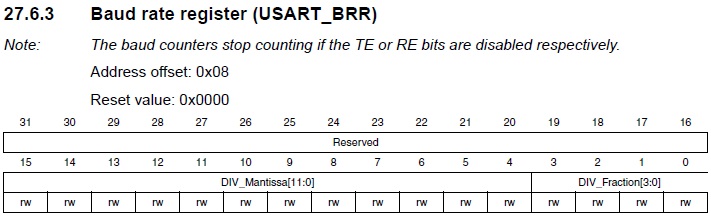

Следующий регистр — регистр настройки скорости передачи данных или бит-рейта (Baud rate register)

Здесь всего два битовых поля:

DIV_Mantissa[11:0] (mantissa of USARTDIV): мантисса или целая часть.

DIV_Fraction[3:0] (fraction of USARTDIV): дробная часть.

Чуть позже мы узнаем, как производится настройка бит-рейта шины USART.

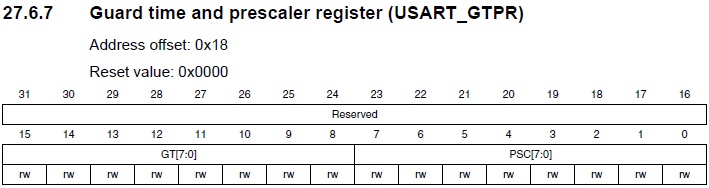

А теперь следующий регистр — регистр времени защиты и предделителей (Guard time and prescaler register)

Здесь также два битовых поля:

GT[7:0] (Guard time value): значение времени защиты в тактах. Используется только в режиме работы со смарткартами.

PSC[7:0] (Prescaler value): значение коэффициента предделителя. Используется только в режиме работы со смарткартами и в режиме ИК

Для режима ИК в режиме пониженного энергопотребления

00000001 — деление на 1

00000010 — деление на 2

В нормальном режиме ИК всегда 00000001.

В режиме работы со смарткартами используются только биты 4:0:

00000 — не используется

00001 — деление на 2

00010 — деление на 4

00011 — деление на 6.

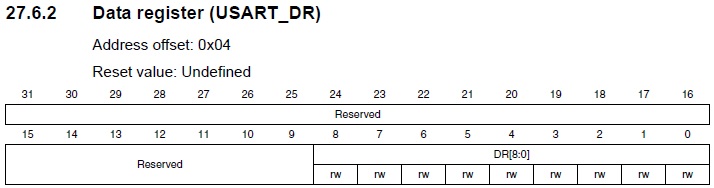

Следующий регистр — регистр данных (Data register)

Используются только 9 младших бит, в данный регистр мы записываем данные для их последующей передачи в шину или читаем из него пришедшие данные.

Давайте теперь рассмотрим, как настраивается скорость работы шины USART.

Для этого существует формула в Reference Manual

![]()

где fCK — частота тактирования периферии (PCLK1 для USART2, 3, 4, 5 или PCLK2 для USART1), а USARTDIV, это коэффициент деления, который содержится в двух битовых полях регистра BRR.

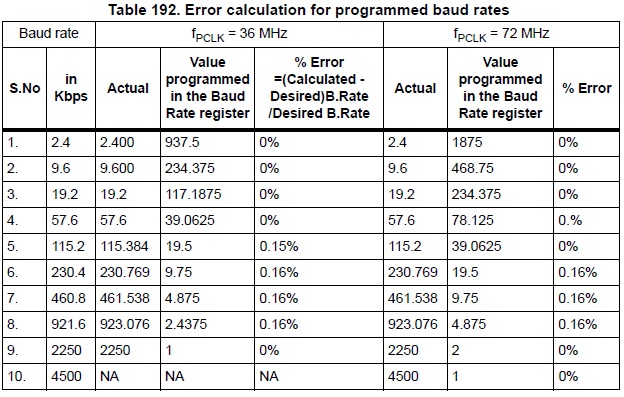

Также в той же технической документации приведены аж целых 3 примера расчёта этого самого коэффициента деления из двух полей.

Нам, думаю хватит и одного. За основу берём 1 пример.

Если в целой части (DIV_Mantissa) находится десятичное число 27, а в дробной 12, то целая часть коэффициента у нас и будет 27, а дробная считается делением числа в дробной части регистра на 16, то есть в нашем случае 12/16 — это 0.75. Таким образом, коэффициент у нас получился 27.75.

Дальше мы уже подставляем этот коэффициент в вышеприведенную формулу и, в зависимости от нашей установленной частоты тактирования шины, рассчитываем наш битрейт.

Так как стандартные общепринятые скорости (9600, 115200 и т.д.) мы не всегда сможем получить точно из формулы, то мы можем рассчитать процент ошибки (или погрешности), в технической документации в качестве примеров расчёта приведена вот такая таблица

Хотя точного значения мы не всегда сможем добиться, но надо стремиться к тому, чтобы погрешность была наименьшей.

В следующей части нашего занятия мы закрепим наши знания, приобретенные в прошлой части занятия, на практике.

Предыдущий урок Программирование МК STM32 Следующая часть

Отладочную плату STM32F103C8T6 можно приобрести здесь STM32F103C8T6

Программатор недорогой можно купить здесь ST-Link V2

Переходник USB to TTL можно приобрести здесь ftdi ft232rl

Индикатор светодиодный семиразрядный с драйвером MAX7219

Логический анализатор 16 каналов можно приобрести здесь

Смотреть ВИДЕОУРОК (нажмите на картинку)

Добавить комментарий