STM Урок 203. Assembler. RCC. Стек. Новые команды. Часть 2

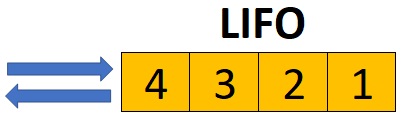

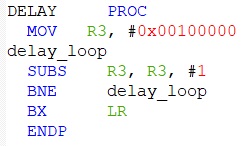

В предыдущей части урока мы подключили новый модуль, познакомились со стеком, а также научились обеспечивать видимость продпрограмм других модулей. Аналогичным образом отключим PLL

|

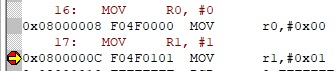

1 2 3 4 5 6 7 8 9 10 11 12 |

BNE wait_cfgrsws ;Clear bit RCC_CR_PLLON in register RCC_CR LDR R2, =(PERIPH_BB_BASE + (RCC_CR - PERIPH_BASE) * 32 + RCC_CR_PLLON_N * 4) STR R0, [R2] LDR R2, =RCC_CR wait_pllrdy_res LDR R3,[R2] ; читаем регистр RCC_CR AND R3, R3, #RCC_CR_PLLRDY CMP R3, #0 BNE wait_pllrdy_res |

Так как очищали мы только один бит, логичнее было применить бит-бэндинг. Выключим HSE и его детектор …

STM Урок 203. Assembler. RCC. Стек. Новые команды. Часть 2 Читать далее »