PIC. Урок 15. Модуль MSSP. Режим SPI. Часть 1

Переходим к следующему модулю — MSSP.

Модуль MSSP (Master Synchronous Serial Port) — синхронная последовательная шина, которая обеспечивает аппаратную поддержку шин SPI и I2C, соответственно, именно в таких режимах она и может работать. Правда данные режимы могут ещё делиться на ведущий и ведомый, также SPI-режим может быть ещё четырёх видов, в зависимости от синхронизации по определённым фронтам тактирования, а также по фазам начала приёма и передачи битов.

Давайте пока познакомимся с общими принципами работы данного модуля, которые будут действительны для обоих заявленных режимов.

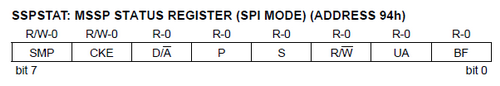

У модуля MSSP есть три основных управляющих регистра — это SSPSTAT, SSPCON и SSPCON2.

Регистр SSPSTAT, являясь в основном регистром состояний модуля, содержит два бита, которые служат для определённых настроек, поэтому его мы также можем отнести к регистрам управления.

Управляющий регистр SSPCON — управляющий регистр, который актуален для обоих режимов работы, а вот дополнительный управляющий регистр SSPCON2 актуален только для режима I2C, поэтому в данном уроке мы его не будем затрагивать, дабы не забивать свои головы лишней информацией, которую мы, когда дойдём до шины I2C, все равно забудем.

Также для общих регистров, которые используются в обоих режимах, мы будем рассматривать их работу именно в режиме SPI.

Но, прежде чем мы начнём изучать регистры, а также блок-схемы и всё прочее модуля MSSP в региме SPI, давайте немного познакомимся вообще с шиной SPI.

Шина SPI (Serial Peripheral Interface) очень широко используется в электронике. Она очень удобна, являясь синхронной и полнодуплексной, поэтому, применяется во многих схемах для общения между различными цифровыми устройствами — датчиками, контроллерами, драйверами и прочими устройствами.

Передача данных как правило происходит по двум проводам, которые обычно называются MOSI и MISO. Также существует ножка для синхронизации SCK, а также ножка выбора устройства SS.

Немного подробнее выводах интерфейса SPI:

SS (chip select) — это ножка выбора устройства. Если на ведомом устройстве на данной ножке установится низкий уровень, то данное устройство будет откликаться и обмениваться информацией по шине SPI, если высокий, то не будет.

MOSI (master output slave input) — это ножка выхода ведущего устройства и входа ведомого устройства.

MISO (master input slave output) — наоборот, выход ведомого, вход ведущего.

SCK — ножка синхронизации. Ко всем устройствам, участвующим в обмене информации по данной шине, подаются синхроимпульсы с определённой частотой.

В обмене информацией по данной шине и по данным двум проводам могут участвовать два или более устройств. Одно из всех устройств обязательно должно быть ведущим (MASTER). Данное устройство является инициатором передачи данных, также оно выбирает с помощью низкого уровня на определённой ножке SS, которых может быть несколько в зависимости от количества устройств, то устройство, с которым ведущее устройство будет обмениваться информацией. Также ведущее устройство передаёт синхронизирующие импульсы на ножке SCK, а остальные устройства, являющиеся ведомыми, импульсов данных не генерируют, а пользуются теми, которые генерирует ведущее устройство.

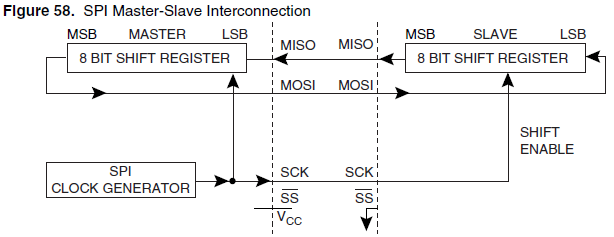

Также важно отметить, что обмен идет побитно, но, как правило, у обменивающихся ведущего и ведомого устройств существуют 16-ти или 8-битные буферы, которые и накапливают в себя, а также отдают побитно информацию. Обмен происходит кольцевым способом

Эта картинка была взята по-моему из даташита контроллера AVR, но она имеет актуальность и для сегодняшнего занятия. Здесь используются буферы 8-битной ширины.

Как только на ножке синхронизации будет определённый фронт, или нисходящий или восходящий, в зависимости от настройки, данные регистры у ведомого и ведущего устройства обменяются информацией, причем не всей информацией, а только одним битом. Данные регистры сдвинутся влево и старшие биты из каждого регистра уйдут в младшие биты такого же регистра сопряженного устройства. То есть ведомый передаст свой старший бит через ножку MOSI ведущему, который его запишет в освободившийся за счет сдвига влево младший бит, а ведомый свой вытесненный за счет сдвига передаст старший бит через ножку MISO в младший бит ведущего. Вот так и идёт обмен, то есть за 8 полных циклов тактирования они полностью обменяются байтами.

Как только все 8 битов обменяются между устройствами, определённый регистр нам просигнализирует о том, что обмен закончен и биты из регистра сдвига или буфера передадутся в другой регистр, с которого мы и будем считывать наш байт.

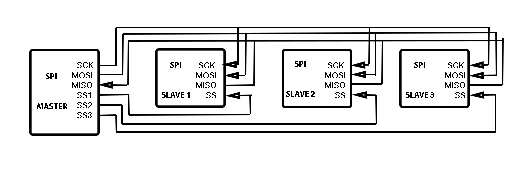

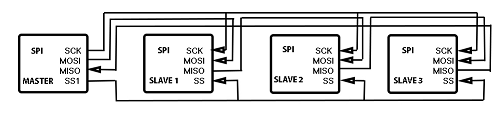

Существует несколько способов обена информацией между несколькими устройствами, то есть когда на одно ведущее устройство приходится несколько ведомых. Мы рассмотрим два самых распространённых из них.

Первый способ — радиальный (нажмите на картинку для увеличения изображения)

Здесь мастер направляет данные к определённому устройству, включая на ножке SS логический 0. При данном способе возможно выбрать только одно устройство, также потребуются несколько свободных ножек портов контроллера.

Есть ещё один интересный способ — кольцевой или каскадный (нажмите на картинку для увеличения изображения)

А с четырьмя видами, или режимами передачи данных по интерфейсу SPI мы познакомимся в процессе изучения организации передачи по SPI в нашем контроллере.

Собственно, пора уже переходить к контроллеру.

Начнём с регистров модуля MSSP, которые так или иначе участвуют в организации передачи по шине SPI.

Начнём с регистра SSPSTAT и рассмотрим назначение его отдельных битов

бит 7: SMP (Sample bit) — фаза выборки бита

Режим ведущего SPI:

1 — входные данные опрашиваются в конце периода вывода данных

0 — входные данные опрашиваются в середине периода вывода данных

Режим ведомого SPI:

Бит SMP всегда должен быть равен 0

бит 6: CKE (SPI Clock Select bit) — Выбор фронта передачи сигнала

Если бит SKP равен 0:

1 — Передача происходит по переднему фронту сигнала на ножке SCK

0 — Передача происходит по заднему фронту сигнала на ножке SCK

Если бит SKP равен 1:

1 — Передача происходит по заднему фронту сигнала на ножке SCK

0 — Передача происходит по переднему фронту сигнала на ножке SCK

бит 5 — D/A (Data/Address bit) — бит данных/адреса

Используется только в режиме I2C.

бит 4 — P (Stop bit) — бит Stop

Используется только в режиме I2C. Сбрасывается в 0, когда модуль MSSP выключен (SSPEN=0)

бит 3 — S (Start bit) — бит Start

Используется только в режиме I2C. Сбрасывается в 0, когда модуль MSSP выключен (SSPEN=0)

бит 2 — R/W (Read/Write bit information) —

Используется только в режиме I2C.

бит 1 — UA (Update Address bit) — флаг обновления адреса устройства

Используется только в режиме I2C.

бит 0 — BF (Buffer Full Status bit) — флаг заполнения буфера

Для режима SPI (только в режиме приёма)

1 — Приём завершен, SSPBUF полон

0 — Приём не завершен, SSPBUF пуст

Для режима I2C используется в режиме приёма и передачи.

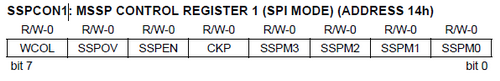

Следующий регистр управления — SSPCON1

бит 7 — WCOL (Write Collision Detect bit) — флаг обнаружения коллизии (в режиме SPI только при передаче)

1 — Попытка записи в регистр SSPBUF в то время, когда он передаёт предыдущее значение (должен быть очищен программно).

0 — Нет коллизии.

бит 6 — SSPOV (Receive Overflow Indicator bit) — флаг переполнения

1 — Получение нового байта в то время, когда регистр SSPBUF всё ещё содержит предыдущие данные. В случае переполнения данные в SSPSR теряются. Переполнение может происходить только в ведомом режиме. Во избежание переполнения нужно прочитать SSPBUF (бит быть очищен программно)

0 — Нет переполнения

В ведущем режиме бит переполнения не устанавливается, так как каждый новый приём (передача) инициируется путём записи значения в регистр SSPBUF.

бит 5 — SSPEN (Synchronous Serial Port Enable bit) — включение модуля MSSP

1 — MSSP включен и ножки SCK, SDO, SDI, и SS сконфигурированы как ножки SSP.

0 — MSSP отключен и ножки сконфигурированы как ножки I/O

При включении ножки должны быть настроены для работы в правильном направлении при помощи регистра TRISxx.

бит 4 — CKP (Clock Polarity Select bit) — бит полярности тактового сигнала

1 — пассивный уровень сигнала высокий

0 — пассивный уровень сигнала низкий

биты 3-0 — SSPM3:SSPM0 (Synchronous Serial Port Mode Select bits) — биты выбора режима работы модуля MSSP

0101 — Ведомый режим SPI, тактирование с ножки SCK. Управление ножкой SS отключено. SS может быть использована как ножка I/O.

0100 — Ведомый режим SPI, тактирование с ножки SCK. Управление ножкой SS включено.

0011 — Ведущий режим SPI, тактирование — выход TMR2 / 2

0010 — Ведущий режим SPI, тактирование — FOSC/64

0001 — Ведущий режим SPI, тактирование — FOSC/16

0000 — Ведущий режим SPI, тактирование — FOSC/4

Для режима I2C комбинации битов здесь не указаны.

Есть ещё один управляющий регистр — SSPCON2. Так как данный регистр актуален только для режима I2C, то в данном уроке он рассматриваться не будет.

В следующей части урока мы рассмотрим блок-схему работы модуля MSSP в режиме SPI, а также с применением нескольких основных режимов шины SPI.

Купить программатор (неоригинальный) можно здесь: PICKit3

Купить программатор (оригинальный) можно здесь: PICKit3 original

Логический анализатор 16 каналов можно приобрести здесь

Смотреть ВИДЕОУРОК в RuTube (нажмите на картинку)

Смотреть ВИДЕОУРОК в YouTube (нажмите на картинку)

Добавить комментарий