STM Урок 150. LL. I2C. Подключаем внешний EEPROM. Часть 1

Сегодня мы попробуем с помощью библиотеки LL поработать с шиной I2C. В качестве подопытного устройства мы возьмём микросхему EEPROM — AT24C32, которая установлена в модуле с часовой микросхемой DS3231 и также в часовом модуле с микросхемой DS1307. С данной микросхемой мы уже работали, когда изучали программирование шины I2C для контроллеров AVR. Там эта шина называлась TWI. Причём микросхему мы использовали с часовым модулем на микросхеме DS1307. Данный модуль мы будем использовать и сегодня.

С данной шиной мы уже очень много работали, поэтому объяснять, как работает данная шина, нет никакого смысла.

Очень подробное объяснение работы шины I2C было в уроке 8, ещё более подробное объяснение было в уроке 16 по МК AVR, а также в уроке 19 по МК PIC. Причём в последнем мы работали именно с микросхемой внешней памяти EEPROM.

Поэтому цель данного урока будет следующая: изучение возможностей микроконтроллера STM32F1 по работе с шиной I2C, а также, что самое главное, изучение возможностей библиотеки LL по работе с данной шиной.

Поэтому равно как и работу шины, работу микросхемы AT24 мы также подробно изучать не будем, так как это давно уже нами изучено. Кто не знает, как работает шина I2C, а также микросхема AT24, смотрите вышеназванные уроки.

В уроке 8 было также рассмотрено устройство шины I2C в контроллере STM32, правда в несколько другой серии, особой разницы между ними в этом плане нет.

Тем не менее давайте посмотрим блок-схему аппаратной реализации шины I2C в контроллере серии STM32F1

Как видим, разницы с контроллером серии STM32F4 в плане реализации шины I2C нет вообще.

Здесь мы видим контакты SDA и SCL, также существуют регистры, которые мы настраиваем для работы, регистр данных, адресный регистр, также регистр двойного адреса, который поддерживает уже 16-битный адрес, два управляющих регистра — CR1 и CR2, регистры статуса — SR1 и SR2, а также регистр, задающий частоту передачи данных или скорость. Есть ещё регистр PEC (Packet error checking) — регистр отслеживания ошибок. Вернее это даже не отдельный регистр, а битовое поле, состоящее из 8 бит регистра SR2, в которое записывается контрольная сумма кадра.

Также давайте рассмотрим поподробнее регистры шины I2C. Регистров у данной шины немало, причём, проведя анализ исходного кода, я обнаружил, что используются они в нашем проекте все без исключения, так что наберитесь терпения.

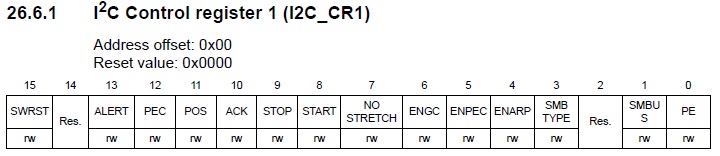

Первый регистр — регистр управления I2C_CR1

В данный регистр входят следующие биты:

SWRST (Software reset): бит программного сброса. В случае наличия в нём логической единицы биты регистров шины сбрасываются в состояние по умолчанию. Данный бит может быть использован в случае возникновения ошибок.

ALERT (SMBus alert): бит разрешения генерации сигнала ALERT при работе шины в режиме SMBus. В случае единицы генерация разрешена.

PEC (Packet error checking): бит обнаружения ошибок. Данный бит устанавливается и сбрасывается программно, но также может быть сброшен аппаратно, когда передаётся PEC, или с помощью условия START или STOP, или когда бит PE равен 0

0 — PEC передаётся

1 — PEC не передаётся.

POS (Acknowledge/PEC Position for data reception): бит положения ACK/PEC в режиме MASTER в двухбайтовой конфигурации. Данный бит устанавливается или сбрасывается программно, а также может быть сброшен аппаратно, когда бит PE равен 0

0 — бит ACK управляет ACK (NACK) текущего байта, получаемого в регистре сдвига. Бит PEC указывает, что текущий байт в регистре сдвига является PEC

1 — бит ACK управляет ACK (NACK) следующего байта, который будет принят в регистре сдвига. Бит PEC указывает, что следующий байт в регистре сдвига является PEC.

ACK (Acknowledge enable): бит разрешения отправки ACK (NACK) после приёма байта данных или адреса. Устанавливается или сбрасывается программно, а также может быть сброшен аппаратно, когда бит PE равен 0

0 — принятый байт не завершается условием ACK (NACK).

1 — принятый байт завершается условием ACK (NACK).

STOP (Stop generation): бит генерации условия STOP

В режиме MASTER

0 — условие STOP не генерируется

1 — генерация STOP после передачи текущего байта или после отправки текущего условия START.

В режиме SLAVE

0 — условие STOP не генерируется

1 — линии SDA и SCL опустятся в 0 после передачи текущего байта.

START (Start generation): бит генерации условия START.

В режиме MASTER

0 — условие START не генерируется

1 — генерация условия START.

В режиме SLAVE

0 — условие START не генерируется

1 — Генерация условия START в случае, если шина I2C свободна.

NOSTRETCH (Clock stretching disable): данный бит используется для отключения увеличения времени в режиме SLAVE, когда установлен флаг ADDR или BTF, до тех пор, пока он не будет сброшен программным обеспечением

0 — передача от MASTER останавливается. Данная возможность используется в том случае, когда SLAVE требуется какое-то время на обработку данных. Ножка SCL прижимается к земле и MASTER будет ждать и не будет ничего посылать до тех пор, пока линия не будет отпущена

1 — отложенный приём отключен.

ENGC (General call enable): бит работы с широковещательным запросом (адрес 0x00)

0 — обработка широковещательных запросов отключена. На обращение по адресу устройства 0x00 генерируется условие NACK.

1 — обработка широковещательных запросов включена. На обращение по адресу устройства 0x00 генерируется условие ACK.

ENPEC (PEC enable): бит включения аппаратного подсчёта CRC

0 — аппаратный подсчёт CRC отключен

1 — аппаратный подсчёт CRC включен.

ENARP (ARP enable): бит включения ARP в режиме SMBus

0 — ARP отключен

1 — ARP включен.

SMBTYPE (SMBus type): бит типа устройства в режиме SMBus

0 — Device

1 — Host.

SMBUS (SMBus mode): режим работы шины

0 — I2C

1 — SMBus.

PE (Peripheral enable): бит включения шины

0 — периферия I2C отключена

1 — периферия включена.

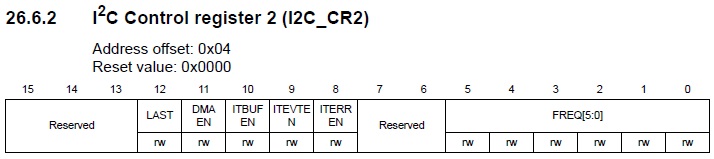

Следующий управляющий регистр — I2C_CR2

Назначение битов данного регистра следующее:

LAST (DMA last transfer): бит разрешения генерации периферией DMA сигнала окончания передачи (EOF)

0 — генерация окончания передачи DMA запрещена

1 — генерация окончания передачи DMA разрешена

DMAEN (DMA requests enable): бит разрешения запросов к периферии DMA

0 — запосы к DMA отключены

1 — запосы к DMA включены, когда любой из флагов TxE или RxNE равен 1.

ITBUFEN (Buffer interrupt enable):

0 — Установка флагов TxE или RxNE не генерирует прерывания

1 — Установка флагов TxE или RxNE генерирует прерывание по данному событию (независимо от состояния бита DMAEN).

ITEVTEN (Event interrupt enable): бит разрешения прерываний по событию

0 — прерывания по событию запрещены.

1 — прерывания по событию разрешены.

ITERREN (Error interrupt enable): бит разрешения прерываний при возникновении ошибок

0 — прерывания при возникновении ошибок запрещены.

1 — прерывания при возникновении ошибок разрешены.

FREQ[5:0] (Peripheral clock frequency): битовое поле для задания частоты тактирования модуля. В данное поле заносится число от 2 до 50.

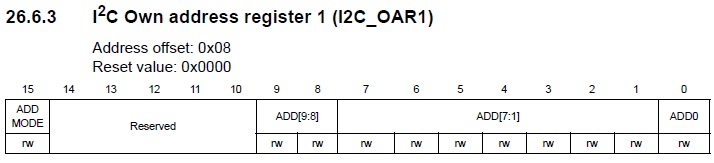

Следующий регистр — первый регистр собственного адреса I2C_OAR1 в режиме SLAVE

Назначение битов данного регистра:

ADDMODE (Addressing mode): режим адресации в режиме SLAVE

0 — 7-разрядный режим адресации (на 10-разрядный адрес не откликается)

1 — 10-разрядный режим адресации (на 10-разрядный адрес откликается).

ADD[9:8] (Interface address): 9 и 8 биты адреса устройства в режиме 10-разрядной адресации.

ADD[7:1] (Interface address): 7:1 биты адреса устройства.

ADD0 (Interface address): 0 бит адреса устройства в режиме 10-битной адресации.

Следующий регистр — второй регистр собственного адреса I2C_OAR2 в режиме SLAVE

Назначение битов регистра:

ADD2[7:1] (Interface address): биты 7:1 альтернативного адреса в режиме двойной адресации.

ENDUAL (Dual addressing mode enable): бит включения режима двойной адресации

0 — режим двойной адресации выключен

1 — режим двойной адресации включен. Устройство откликается на альтернативный адрес.

ADD2[7:1] (Interface address):

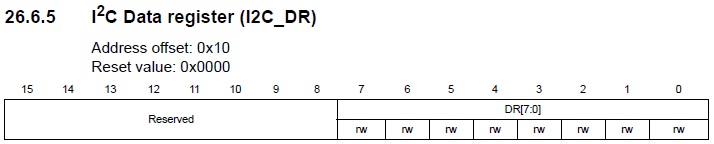

Следующий регистр — регистр хранения данных I2C_DR

В данный регистр записывается принятый байт в случае приёма, а в случае передачи мы сюда пишем данные, которые хотим передать.

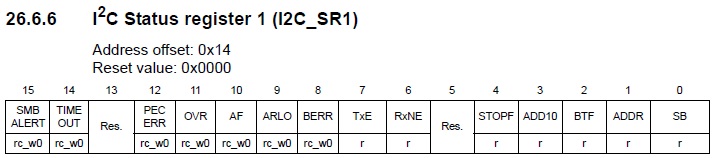

Следующий регистр — регистр состояния I2C_SR1

Назначение битов данного регистра:

SMBALERT (SMBus alert): флаг события ALERT в режиме SMBus.

TIMEOUT (Timeout or Tlow error): флаг события при продолжительном времени нахождения ножки SCL прижатой к земле. В случае MASTER — 10 милисекунд, SLAVE — 25 милисекунд

0 — таймаут не истёк

1 — таймаут истёк

PECERR (PEC Error in reception): флаг ошибки PEC при приёме

0 — нет ошибки

1 — обнаружена ошибка PEC.

OVR (Overrun/Underrun): флаг переполнения данных

0 — переполнения не было

1 — произошло событие переполнения данных

AF (Acknowledge failure): отсутствие подтверждения ACK

0 — нормальное подтверждение (ACK)

1 — отсутствие подтверждения (NACK). Для сброса нужно записать 0.

ARLO (Arbitration lost): бит потери арбитража в режиме MASTER

0 — потери арбитража не обнаружено

1 — потеря арбитража. Для сброса нужно записать 0.

BERR (Bus error): флаг ошибки шины в плане установки условия START или STOP на шине в ненужный момент

0 — ошибки не было

1 — обнаружена ошибка.

TxE (Data register empty): флаг очистки регистра данных в режиме передачи. Устанавливается, когда из регистра данных DR данные переместятся в сдвиговый регистр.

0 — регистр данных не пустой

1 — регистр данных пуст.

RxNE (Data register not empty): флаг очистки регистра данных в режиме приёма. Устанавливается, когда данные появились в регистре.

0 — регистр данных пуст

1 — регистр данных не пустой.

STOPF (Stop detection): флаг появления условия STOP на шине в режиме SLAVE. Для сброса нужно прочитать регистр SR1 и произвести запись в CR1.

0 — обнаружено условие STOP

1 — условие STOP не обнаружено.

ADD10 (10-bit header sent): флаг отправки 10-битного адреса в режиме MASTER

0 — событие отправки 10-битного адреса не обнаружено

1 — произошла отправка первого байта 10-битного адреса.

BTF (Byte transfer finished): флаг окончания приёма/передачи байта. Работает только при NOSTRETCH=0

0 — событие окончания приёма/передачи байта не происходило

1 — произошло событие окончания приёма/передачи байта.

ADDR (Address sent): Устанавливается после передачи адреса в режиме MASTER, а в режиме SLAVE — при совпадении пришедшего от MASTER адреса с собственным. Для сброса надо сначала прочитать регистр SR1, а потом и SR2.

SB (Start bit): Флаг возникновения сигнала START в режиме MASTER

0 — условие START не обнаружено

1 — обнаружено условие START.

Следующий регистр — регистр состояния I2C_SR2

Назначение битов регистра:

PEC[7:0] (Packet error checking register): битовое поле, в которое записывается контрольная сумма кадра при ENPEC=1.

DUALF (Dual flag): флаг обнаружения альтернативного адреса на шине в режиме SLAVE

0 — альтернативный адрес не обнаружен

1 — произошло совпадение запрошенного адреса с собственным альтернативным.

SMBHOST (SMBus host header): флаг приёма заголовка SMBus Host в режиме Device

0 — заголовок не принимался

1 — принят заголовок

SMBDEFAULT (SMBus device default address): бит приёма адреса по умолчанию в режиме Device для SMBus-устройства

0 — адрес по умолчанию не принимался

1 — принят адрес по умолчанию.

GENCALL (General call address): флаг приёма широковещательного адреса в режиме SLAVE

0 — широковещательный адрес не принимался

1 — принят широковещательный адрес

TRA (Transmitter/receiver): режим работы (приёмник/передатчик)

0 — данные приняты

1 — данные отправлены.

BUSY (Bus busy): флаг занятости шины

0 — шина свободна

1 — шина занята.

MSL (Master/slave): режим работы (MASTER/SLAVE)

0 — шина работает в режиме SLAVE

1 — шина работает в режиме MASTER, включается аппаратно, когда модуль переводится в режим MASTER при помощи установки бита SB, сбрасывается тоже аппаратно.

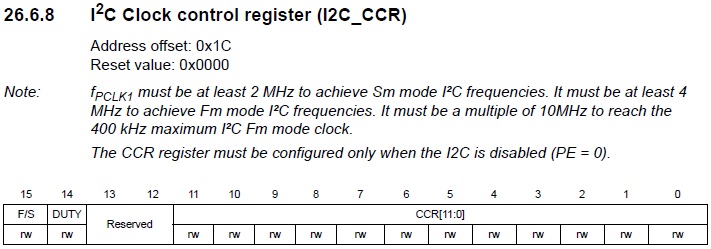

Следующий регистр — регистр управления частотой работы шины I2C_CCR

Назначение битов:

F/S (I2C master mode selection): бит установки скоростного режима

0 — режим Standard

1 — режим Fast.

DUTY (Fm mode duty cycle): Данный бит устанавливает скважность шины в режиме Fast

0 — отношение времени низкого состояния к времени высокого состояния 2

1 — отношение времени низкого состояния к времени высокого состояния 16/9

CCR[11:0] (Clock control register in Fm/Sm mode): битовое поле частоты работы шины в режиме MASTER для режимов Standard и Fast

Время высокого и низкого состояния ножки SCL рассчитывается следующим образом.

В режиме Standard:

Thigh = Tlow = CCR * TPCLK1

В режиме Fast

Если DUTY=0:

Thigh = CCR * TPCLK1

Tlow = 2 * CCR * TPCLK1

Если DUTY=1:

Thigh = 9 * CCR * TPCLK1

Tlow = 16 * CCR * TPCLK1.

Следующий регистр — регистр управления времени нарастания фронта I2C_TRISE

TRISE[5:0] (Maximum rise time in Fm/Sm mode): значение для расчёта времени нарастания фронта. Данное значение сначала надо рассчитать по формуле

T = TrMAX / TPCLK1 + 1

TrMAX для режима Standard составляет 1000 наносекунд, а для режима Fast — 300.

Вот, наконец-то, мы немного разобрались со всеми регистрами, задействованными в работе шины I2C в нашем контроллере.

В следующей части нашего урока мы настроим проект, а также изучим подробно, каким образом происходит инициализация модуля I2C.

Отладочную плату STM32F103C8T6 можно приобрести здесь STM32F103C8T6

Программатор недорогой можно купить здесь ST-Link V2

Модуль RTC DS3231 с микросхемой памяти (2-5 шт)

Модуль RTC DS3231 с микросхемой памяти (1 шт) — так дороже

Семисегментный чертырехразрядный индикатор красный (с общим анодом или катодом на выбор) 10 шт

Логический анализатор 16 каналов можно приобрести здесь

Смотреть ВИДЕОУРОК в RuTube (нажмите на картинку)

Смотреть ВИДЕОУРОК в YouTube (нажмите на картинку)

доброе время суток.

у меня есть маленький вопрос

а как можно задать частоту не 100КГц-400КГц а к примеру 1КГц