STM Урок 166. CMSIS. STM32F1. RCC. Часть 1

В прошлом занятии мы начали (вернее продолжили) курс по программированию контроллеров STM с использованием библиотеки интерфейсов CMSIS. Нам удалось настроить некоторые ножки портов с целью помигать светодиодами, подключенными к ним, предварительно включив тактирование определённой периферии. Тактированием этим управляет модуль RCC, который мы заставили включить тактирование на два порта ввода вывода и на модуль AFIO. Но, для того, чтобы нормально управлять тактированием различной периферии, необходимо данный модуль RCC предварительно правильно настроить, чтобы хотя бы знать, какая частота тактирования и где у нас будет.

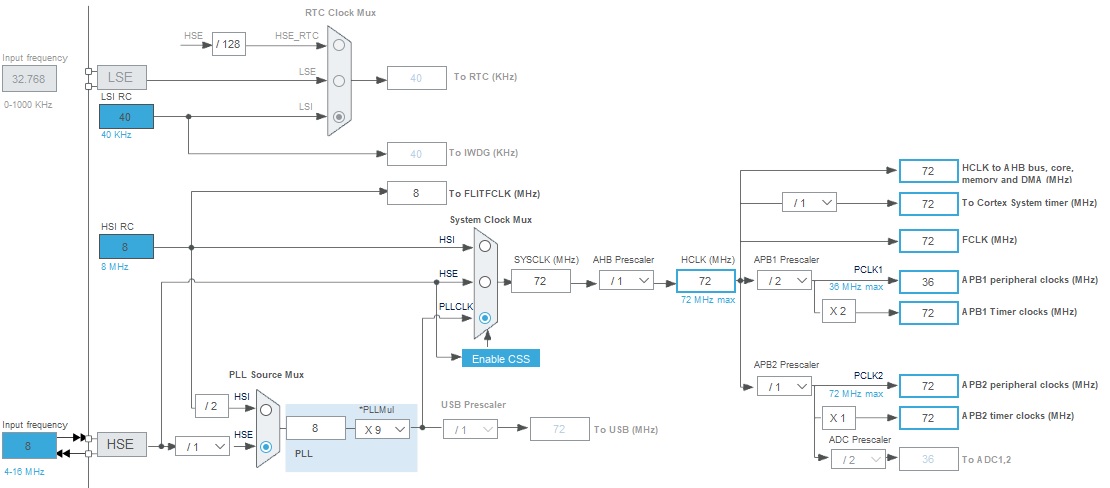

Ранее мы не вдавались сильно в настройки RCC при использовании библиотек HAL и LL, так как данные функции брал на себя проектогенератор Cube MX. Но мы все равно во вкладке Clock Configuration тактирование настраивали, пусть визуально, без использования регистров, но, тем, не менее мы уже немного знакомы с тем, какие есть делители, умножители, мультиплексоры в модуле RCC.

Посмотрим, например на настроенное тактирование в проекте недавнего урока 164 по интерфейсу USART с применением DMA

Здесь мы видим, что необходимо включить, чтобы тактирование завелось от кварцевого резонатора, и чтобы частота HCLK достигла максимальных 72 мегагерца. Вот это и будет нашей целью, а эта настройка нам будет служить подсказкой, какие значения делителей и умножителей использовать и какой переключатель (мультиплексор) в какое положение включать.

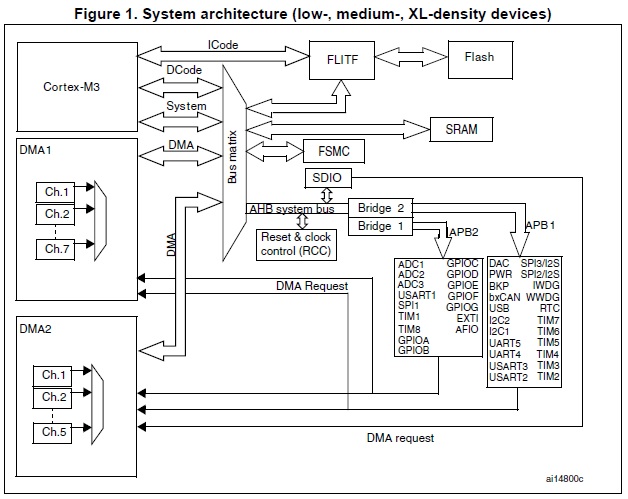

Теперь откроем техническую документацию на наш контроллер STM32F1xx, так как мы будем его же и использовать и посмотрим для начала блок-схему, в которой видны все делители и умножители с возможными значениями и также многое другое, в подробности мы вдаваться не будем. Регистры автор документации, скорее всего, не вносил сюда из-за того, что схема и так очень информативна и чтобы нас сильно не запутать

Первым делом мы должны знать, что существует два основных вида тактирования — от внутреннего генератора контроллера — HSI (high speed internal clock signal) и от внешнего — HSE (high speed external clock signal). Так как у нас на плате установлен кварцевый резонатор на 8 МГц, то мы будем пользоваться внешним — HSE. Резонатор обеспечивает более стабильное тактирование, а также при использовании внутреннего тактирования (HSI) ввиду применения нерегулируемого делителя на 2 мы максимальной частоты работы не добьёмся.

Есть также подобные низкоскоростные модули тактирования LSI и LSE, используемые для модуля RTC (real-time clock), с которым мы будем работать в более поздних уроках.

Смысла подробного изучения каждого подмодуля в RCC нет, так как настраивать мы их будем не все и голову лишним себе пока забивать не будем.

Приступим теперь к регистрам, которых также у RCC много, все мы их также рассматривать не будем, рассмотрим те, которые мы будем использовать в проекте данного урока. Например, регистры, отвечающие за перезагрузку тех или иных модулей, нам будут не нужны и также регистры, которые отвечают за включение тактирования различных модулей, мы тоже не будем рассматривать, так как там всё очень просто, всю информацию несут в себе наименования битов данных регистров.

Первый регистр RCC, рассматриваемый нами — управляющий регистр

Теперь раздельно рассмотрим различные биты и битовые поля данного регистра

PLLRDY (PLL clock ready flag): флаг готовности PLL. Устанавливается аппаратно для блокирования RCC

0 — PLL разблокирован

1 — PLL заблокирован.

PLLON (PLL enable): бит разрешения работы PLL

0 — PLL отключен

1 — PLL задействован.

CSSON (Clock security system enable): бит разрешения работы детектора тактового сигнала от HSE

0 — детектор отключен

1 — детектор включен.

HSEBYP (External high-speed clock bypass): бит разрешения использования внешнего генератора. Возможно использование только при включенном бите HSEON

0 — внешнее тактирование запрещено

1 — внешнее тактирование разрешено

HSERDY (External high-speed clock ready flag): бит, гласящий о том, что внешнее тактирование стабилизировано. Устанавливается аппаратно

0 — внешний генератор не готов

1 — внешний генератор готов.

HSEON (HSE clock enable): Принудительное включение внешнего тактирования (HSE). Устанавливается и сбрасывается программно

0 — HSE выключен

1 — HSE включен.

HSICAL[7:0] (Internal high-speed clock calibration): битовое поле калибровки. Эти биты инициализируются автоматически при старте. Доступны только для чтения.

HSITRIM[4:0] (Internal high-speed clock trimming): битовое поле, значение битов которого прибавляется к значению HSICAL, с помощью чего появляется возможность корректирования частоты тактирования, которая, как известно, иногда может уходить от ряда условий (окружающая температура, напряжение питания и т.д.). Данные биты работают и на чтение и на запись.

HSIRDY (Internal high-speed clock ready flag): бит, гласящий о том, что внутреннее тактирование стабилизировано. Устанавливается аппаратно

0 — внутренний генератор не готов

1 — внутренний генератор готов.

HSION (Internal high-speed clock enable): бит принудительного запуска внутреннего генератора 8 МГц. Устанавливается и сбрасывается программно, но существуют ситуации, такие как, например, при выходе из некоторых режимов пониженного энергопотребления. Также его невозможно сбросить, если системное тактирование задействовано от внешнего генератора

0 — HSI выключен

1 — HSI включен.

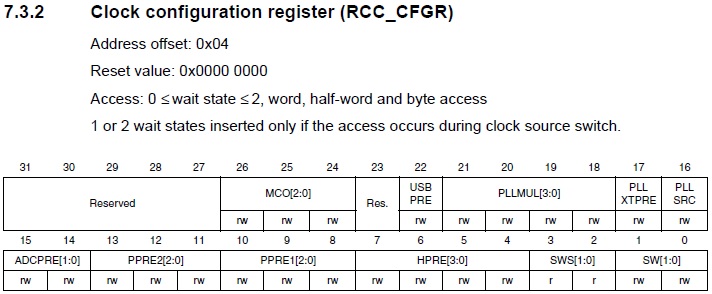

Следующий регистр — конфигурационный

Назначение отдельных битов и битовых полей данного регистра

MCO (Microcontroller clock output): битовое поле назначения вывода MCO. Данные биты устанавливаются и сбрасываются программно

0xx — Не используется (не тактируется)

100 — Совпадает с частотой тактирования системной шины (SYSCLK)

101 — Подключен к HSI

110 — Подключен к HSE

111 — Тактируется с частотой PLLCLK / 2

USBPRE (USB prescaler): включение предделителя для USB

0 — PLLCLK / 1.5

1 — PLLCLK

PLLMUL (PLL multiplication factor): данное битовое поле задаёт коэффициент умножения частоты для PLL

0000 — PLL input clock x 2

0001 — PLL input clock x 3

0010 — PLL input clock x 4

0011 — PLL input clock x 5

0100 — PLL input clock x 6

0101 — PLL input clock x 7

0110 — PLL input clock x 8

0111 — PLL input clock x 9

1000 — PLL input clock x 10

1001 — PLL input clock x 11

1010 — PLL input clock x 12

1011 — PLL input clock x 13

1100 — PLL input clock x 14

1101 — PLL input clock x 15

1110 — PLL input clock x 16

1111 — PLL input clock x 16

PLLXTPRE (HSE divider for PLL entry): предделитель перед PLL

0 — не используется

1 — частота HSE перед подачей в PLL делится на 2.

PLLSRC (PLL entry clock source): используемый вход мультиплексора входа PLL

0 — частота HSI, разделенная на 2

1 — частота HSE.

ADCPRE (ADC prescaler): данное битовое поле определяет коэффициент деления для АЦП

00 — PCLK2 / 2

01 — PCLK2 / 4

10 — PCLK2 / 6

11 — PCLK2 / 8

PPRE2 (APB high-speed prescaler (APB2)): данное битовое поле определяет коэффициент деления для APB2

0xx — HCLK без деления

100 — HCLK / 2

101 — HCLK / 4

110 — HCLK / 8

111 — HCLK / 16

APB (low-speed prescaler (APB1)): данное битовое поле определяет коэффициент деления для APB1

0xx — HCLK без деления

100 — HCLK / 2

101 — HCLK / 4

110 — HCLK / 8

111 — HCLK / 16

HPRE (AHB prescaler): данное битовое поле определяет коэффициент деления для AHB

0xxx — SYSCLK без деления

1000 — SYSCLK / 2

1001 — SYSCLK / 4

1010 — SYSCLK / 8

1011 — SYSCLK / 16

1100 — SYSCLK / 32

1101 — SYSCLK / 64

1110 — SYSCLK / 128

1111 — SYSCLK / 256.

SWS (System clock switch status): данное битовое поле используется только для чтения и показывает, какой источник используется для системного тактирования, следовательно, его биты устанавливаются и сбрасываются аппаратно

00 — HSI

01 — HSE

10 — для тактирования используется PLL

11 — не используется.

SW (System clock switch): с помощью битов данного поля можно выбрать источник для системного тактирования

00 — HSI

01 — HSE

10 — PLL

11 — не используется.

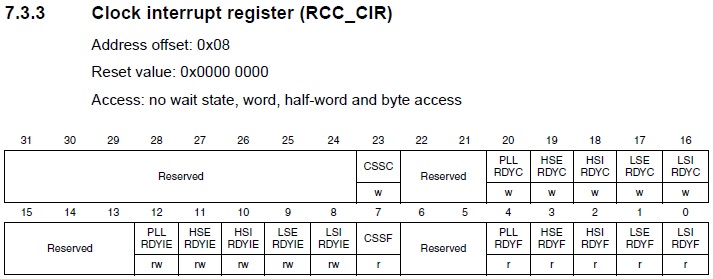

Следующий регистр — регистр прерываний от RCC

Назначение отдельных битов данного регистра

CSSC (Clock security system interrupt clear): бит очистки флага CSSF с помощью записи в него 1

0 — нет эффекта

1 — сброс флага CSSF.

PLLRDYC (PLL ready interrupt clear): бит очистки флага PLLRDYF с помощью записи в него 1

0 — нет эффекта

1 — сброс флага PLLRDYF.

HSERDYC (HSE ready interrupt clear): бит очистки флага готовности HSE с помощью записи в него 1

0 — нет эффекта

1 — сброс флага HSERDYF.

HSIRDYC (HSI ready interrupt clear): бит очистки флага готовности HSI с помощью записи в него 1

0 — нет эффекта

1 — сброс флага HSIRDYF.

LSERDYC (LSE ready interrupt clear): бит очистки флага готовности LSE с помощью записи в него 1

0 — нет эффекта

1 — сброс флага LSERDYF.

LSIRDYC (LSI ready interrupt clear): бит очистки флага готовности LSI с помощью записи в него 1

0 — нет эффекта

1 — сброс флага LSIRDYF.

PLLRDYIE (PLL ready interrupt enable): бит разрешения прерываний при подключении PLL

0 — прерывания запрещены

1 — прерывания разрешены.

HSERDYIE (HSE ready interrupt enable): бит разрешения прерываний по готовности HSE

0 — прерывания запрещены

1 — прерывания разрешены.

HSIRDYIE (HSE ready interrupt enable): бит разрешения прерываний по готовности HSI

0 — прерывания запрещены

1 — прерывания разрешены.

LSERDYIE (HSE ready interrupt enable): бит разрешения прерываний по готовности LSE

0 — прерывания запрещены

1 — прерывания разрешены.

LSIRDYIE (HSE ready interrupt enable): бит разрешения прерываний по готовности LSI

0 — прерывания запрещены

1 — прерывания разрешены.

CSSF (Clock security system interrupt flag): флаг отказа HSE

0 — прерывания по отказу HSE не обнаружено

1 — произошло прерывание по отказу HSE.

PLLRDYF (PLL ready interrupt flag)): флаг прерывания по подключению PLL

0 — прерывания по подключению PLL не обнаружено

1 — произошло прерывание по подключению PLL.

HSERDYF (HSE ready interrupt flag): флаг прерывания по готовности HSE

0 — прерывания по готовности HSE не обнаружено

1 — произошло прерывание по готовности HSE.

HSIRDYF (HSI ready interrupt flag): флаг прерывания по готовности HSI

0 — прерывания по готовности HSI не обнаружено

1 — произошло прерывание по готовности HSI.

LSERDYF (LSE ready interrupt flag): флаг прерывания по готовности LSE

0 — прерывания по готовности LSE не обнаружено

1 — произошло прерывание по готовности LSE.

LSIRDYF (LSI ready interrupt flag): флаг прерывания по готовности LSI

0 — прерывания по готовности LSI не обнаружено

1 — произошло прерывание по готовности LSI.

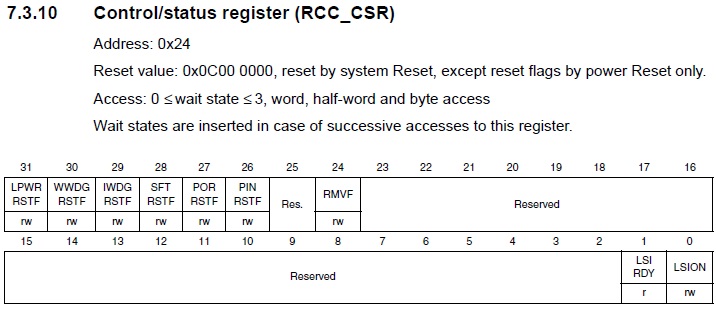

Следующий регистр — управления и статуса

Назначение битов данного регистра

LPWRRSTF (Low-power reset flag): флаг сброса от контроллера пониженного энергопотребления. Устанавливается аппаратно, сбрасывается установкой бита RMVF

0 — сброса от контроллера пониженного энергопотребления не обнаружено

1 — произошел сброс от контроллера пониженного энергопотребления.

WWDGRSTF (Window watchdog reset flag): флаг сброса от оконного сторожевого таймера. Устанавливается аппаратно, сбрасывается установкой бита RMVF

0 — сброса от оконного сторожевого таймера не обнаружено

1 — произошел сброс от оконного сторожевого таймера.

IWDGRSTF (Independent watchdog reset flag): флаг сброса от независимого сторожевого таймера. Устанавливается аппаратно, сбрасывается установкой бита RMVF

0 — сброса от независимого сторожевого таймера не обнаружено

1 — произошел сброс от независимого сторожевого таймера.

SFTRSTF (Software reset flag): флаг программного сброса. Устанавливается аппаратно, сбрасывается установкой бита RMVF

0 — программного сброса не обнаружено

1 — произошел программный сброс.

PORRSTF (POR/PDR reset flag): флаг сброса по срабатыванию и перезагрузке от превышения или принижения порогов супервизора. Устанавливается аппаратно, сбрасывается установкой бита RMVF

0 — срабатывания супервизора не обнаружено

1 — произошел сброс от супервизора по питанию.

PINRSTF (PIN reset flag): флаг сброса от кнопки NRST. Устанавливается аппаратно, сбрасывается установкой бита RMVF

0 — сброса от кнопки NRST не обнаружено

1 — произошел сброс от кнопки NRST.

RMVF (Remove reset flag): бит сброса всех описанных выше флагов. Устанавливается аппаратно для очистки флагов

0 — нет эффекта

1 — программный сброс всех вышеописанных флагов.

LSIRDY (Internal low-speed oscillator ready): бит, гласящий о том, что тактирование внутреннего низкочастотного генератора 40 КГц стабилизировано. Устанавливается аппаратно

0 — внутренний низкочастотный генератор не готов

1 — внутренний низкочастотный генератор готов.

LSION (Internal low-speed oscillator enable)): бит принудительного запуска внутреннего генератора 40 КГц. Устанавливается и сбрасывается программно, но существуют ситуации, такие как, например, при выходе из некоторых режимов пониженного энергопотребления. Также его невозможно сбросить, если системное тактирование задействовано от внешнего генератора

0 — LSI выключен

1 — LSI включен.

Не хватает только битов готовности и включения LSE. Они находятся в регистре RCC_BDCR, не рассматриваемом нами в рамках данного занятия.

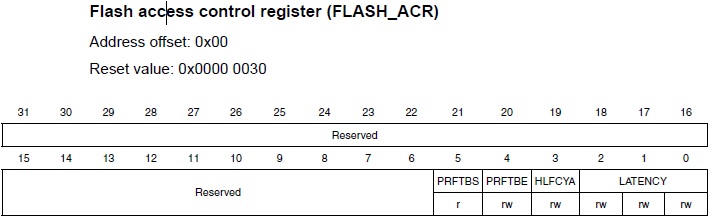

Также рассмотрим один из регистров, работающих с памятью FLASH, встроенной в контроллер.

Хотя, если мы с памятью FLASH не собираемся работать, то есть обращаться к ней во время работы программы, настраивать работу FLASH не нужно, но, по некой сложившейся традиции, мы это как правило делаем, когда настраиваем системную частоту.

Нам нужен будет только регистр управления FLASH

Здесь битов немного, поэтому мы быстренько сейчас их изучим

PRFTBS (Prefetch buffer status): бит состояния буфера предварительной выборки. Бит работает только на чтение

0 — буфер отключен

1 — буфер включен.

PRFTBE (Prefetch buffer enable): бит включения буфера предварительной выборки. Бит работает уже и на чтение и на запись. С помощью него мы можем включить или отключить использования буфера предварительной выборки

0 — буфер отключен

1 — буфер включен.

HLFCYA (Flash half cycle access enable): бит включения доступа к половинному циклу

0 — доступ запрещён

1 — доступ разрешён.

LATENCY (Latency): битовое поле управления задержкой. Данный бит представляет собой отношение периода такта системной частоты (SYSCLK) к времени доступа к FLASH

000 — нет задержки, рекомендуется при системной частоте от 0 до 24 МГц

001 — задержка 1 цикл, рекомендуется при системной частоте от 24 МГц до 48 МГц

010 — задержка 2 цикла, рекомендуется при системной частоте от 48 МГц до 72 МГц.

На данный момент, думаю, нам хватит рассмотренных нами выше регистров, поэтому теперь впору приступить уже и к проекту, который мы создадим и напишем к нему код в следующей части нашего урока.

Отладочную плату STM32F103C8T6 можно приобрести здесь STM32F103C8T6

Программатор недорогой можно купить здесь ST-Link V2

Смотреть ВИДЕОУРОК в RuTube (нажмите на картинку)

Смотреть ВИДЕОУРОК в YouTube (нажмите на картинку)

Добавить комментарий