STM Урок 185. LL. STM32F1. ADC. Regular Once. Часть 1

Давно мы не занимались с такой периферией микроконтроллера, как АЦП (Аналого-цифровой преобразователь) или ADC (Analog-to-digital converter). Думаю, сейчас самое время. Тем более, что, изучая возможности библиотеки LL, мы незаслуженно пропустили столь важную часть архитектуры контроллера.

С данной периферией мы раньше работали и исследовали очень немало её возможностей. Но их, во-первых, гораздо больше, чем мы проходили в уроках 16-21, а, во-вторых, мы работали с АЦП с использованием библиотеки HAL.

Теперь же пришло время поработать с АЦП посерьёзнее и изучить поглубже её аппаратную часть. В этом нам поможет техническая документация, а также и библиотека LL, с помощью функций и макросов которой мы более подробно изучим инициализацию и работу с АЦП.

Прежде чем начать работать со схемой и проектом, нам необходимо будет запастись определёнными знаниями архитектуры АЦП контроллера STM32F1, а также регистров одноимённого модуля.

В контроллере (а подразумевать я буду конкретно контроллер, с которым мы работаем, а именно STM32F103C8) имеется в наличии два модуля АЦП разрешением 12 бит. Каждый из этих модулей способен работать с 16 каналами внешними и двумя внутренними, из которых на нашем контроллере физически доступны 10, а также 2 внутренних.

Также из характеристик хочется выделить, что каждый модуль АЦП нашего контроллера способен развить скорость до 1 мегасэмпла в секунду (Msps), работать с опорным напряжением от 2,4 до 3,6 вольт, но не превышающем напряжение питания, работать с прерываниями по окончанию преобразований, с преобразованиями регулярными и инжектированными, прерываниями от оконного компаратора, с DMA, с одиночными и непрерывными преобразованиями, в том числе с непрерывными по заранее заданному списку очерёдности сканирования каналов, поддерживает автокалиборовку, может выравнивать результат по правому и левому краю.

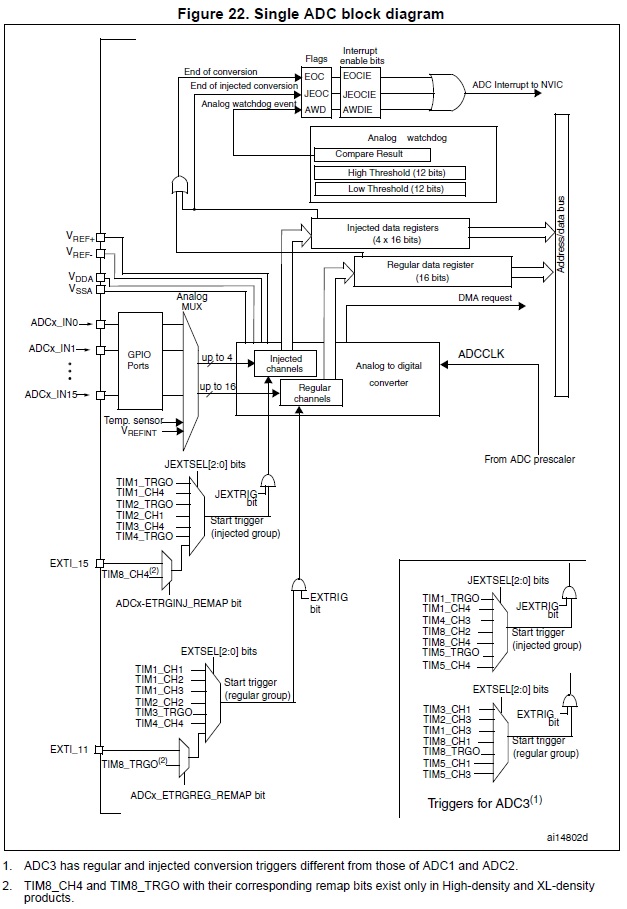

Посмотрим структурную схему одного из модулей АЦП

Каналы модуля АЦП делятся на регулярные и инжектированные. Количество регулярных каналов — 18, при этом результат преобразования всех каналов хранится в одном единственном регистре, вследствие чего приходится часто сохранять результаты преобразования из регистров. Инжектированных каналов мы можем настроить в количестве до четырёх, но зато при этом результат преобразования каждого канала сохраняется в отдельном регистре, то есть каждый канал имеет свой регистр для сохранения результата.

Также хочется отметить, что наши АЦП мы можем настроить для работы в парном режиме.

Также мы можем настроить АЦП в режиме аналогового сторожа (Analog Watchdog).

Ещё мы можем использовать очень много режимов работы АЦП: однократное преобразование канала, длительное преобразование (сканирование не останавливается после преобразования, а начинается заново), автоматическое поочерёдное сканирование нескольких каналов (можно задавать свою очерёдность с помощью списка), многоканальное длительное преобразование, запуск преобразования от внешнего триггера.

Также существует немало режимов в случае использования парной работы двух модулей АЦП. Но эту тему мы пока не будем рассматривать, нам и независимой хватит.

Поэтому давайте немного разберём регистры модулей АЦП. Разбирать мы будем стараться пока те регистры, которые непосредственно будут нам нужны для сегодняшнего урока, а именно для работы с АЦП в регулярном одиночном режиме. А всего регистров я насчитал целых 14.

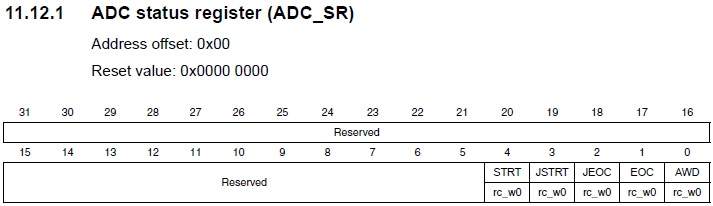

Начнём с регистра состояния

Теперь побитно.

STRT (Regular channel Start flag): бит запуска регулярного преобразования. Устанавливается аппаратно в 1 при начале регулярного преобразования. Сбрасывается программно

0 — регулярное преобразование не было запущено

1 — регулярное преобразование запущено.

JSTRT (Injected channel Start flag): бит запуска инжектированного преобразования. Устанавливается аппаратно в 1 при начале инжектированного преобразования. Сбрасывается программно

0 — инжектированное преобразование не было запущено

1 — инжектированное преобразование запущено.

JEOC (Injected channel end of conversion): бит окончания инжектированного преобразования. Устанавливается аппаратно в 1 в момент окончания инжектированного преобразования. Сбрасывается программно

0 — инжектированное преобразование не завершено

1 — инжектированное преобразование завершено.

EOC (End of conversion): бит окончания группового преобразования. Устанавливается аппаратно в 1 в момент окончания регулярного или инжектированного преобразования. Сбрасывается программно

0 — групповое преобразование не завершено

1 — групповое преобразование завершено.

AWD (Analog watchdog flag): бит состояния оконного компаратора. Устанавливается аппаратно в 1, когда результат преобразования вышел за нижнюю (ADC_LTR) или верхнюю (ADC_HTR) границу окна компаратора

0 — событие от оконного компаратора не зарегистрировано

1 — произошло событие пересечения верхнего или нижнего порога компаратора.

Следующий регистр — первый регистр управления

Назначение битов и битовых полей регистра:

AWDEN (Analog watchdog enable on regular channels): бит разрешения подключения оконного компаратора к регулярным каналам. Установка данного бита, также как и его сброс, производятся программно

0 — подключение оконного компаратора запрещено

1 — подключение оконного компаратора разрешено.

JAWDEN (Analog watchdog enable on injected channels): бит разрешения подключения оконного компаратора к инжектированным каналам. Установка данного бита, также как и его сброс, производятся программно

0 — подключение оконного компаратора запрещено

1 — подключение оконного компаратора разрешено.

DUALMOD[3:0] (Dual mode selection): битовое поле режима совместной работы двух АЦП

0000 — независимый режим

0001 — комбинированный регулярный однократный + инжектированный однократный режимы

0010 — комбинированный регулярный однократный + альтернативный триггерный режимы

0011 — комбинированный инжектированный однократный + быстрый режим чередования

0100 — комбинированный инжектированный однократный + медленный режим чередования

0101 — только инжектированный однократный режим

0110 — только регулярный однократный режим

0110 — только быстрый режим чередования

1000 — только медленный режим чередования

1001 — только альтернативный триггерный режим.

DISCNUM[2:0] (Discontinuous mode channel count): количество регулярных каналов в прерывистом режиме

000 — 1 канал

001 — 2 канала

…

111 — 8 каналов.

JDISCEN (Discontinuous mode on injected channels): бит включения прерывистого (дискретного) режима группы инжектированных каналов

0 — режим выключен

1 — режим включен.

DISCEN (Discontinuous mode on regular channels): бит включения прерывистого (дискретного) режима группы регулярных каналов

0 — режим выключен

1 — режим включен.

JAUTO (Automatic Injected Group conversion): бит включения непрерывного режима группы инжектированных каналов

0 — режим выключен

1 — режим включен.

AWDSGL (Enable the watchdog on a single channel in scan mode): бит включения режима сканирования оконного сторожевого таймера

0 — сканируются все каналы

1 — сканируется канал, настроенный в битовом поле AWDCH[4:0].

SCAN (Scan mode): режим сканирования каналов по списку, определённому либо битовым полем ADC_SQRx, либо ADC_JSQRx

0 — режим выключен

1 — режим включен.

JEOCIE (Interrupt enable for injected channels): разрешение прерываний по окончанию преобразования инжектированных каналов

0 — прерывания запрещены

1 — прерывания разрешены.

AWDIE (Analog watchdog interrupt enable): разрешение прерываний по сигналу оконного компаратора

0 — прерывания запрещены

1 — прерывания разрешены.

EOCIE (Interrupt enable for EOC): разрешение прерываний по окончанию преобразования

0 — прерывания запрещены

1 — прерывания разрешены.

AWDCH[4:0] (Analog watchdog channel select bits): выбор канала для оконного компаратора. Данный бит актуален только при установленном бите AWDSGL

00000 — канал 0

00001 — канал 1

…

10001 — канал 17.

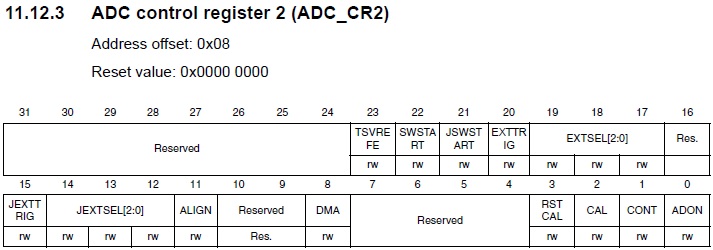

Второй регистр управления

Назначение битов:

TSVREFE (Temperature sensor and VREFINT enable): включает датчик температуры и источник опорного напряжения (ИОН), при условии если они есть в АЦП

0 — датчик температуры и ИОН отключены

1 — датчик температуры и ИОН включены.

SWSTART (Start conversion of regular channels): запуск преобразования регулярных каналов. Этот бит устанавливается программно перед началом запуска преобразования и сбрасывается аппаратно, как только начнётся преобразование. Запускает преобразование регулярных каналов, если SWSTART выбран в качестве события запуска битами EXTSEL[2:0]

1 — запуск преобразования регулярных каналов

0 — бит аппаратно сброшен перед началом преобразования.

JSWSTART (Start conversion of injected channels): запуск преобразования инжектированных каналов. Этот бит устанавливается программно перед началом запуска преобразования и сбрасывается аппаратно, как только начнётся преобразование. Запускает преобразование инжектированных каналов, если JSWSTART выбран в качестве события запуска битами JEXTSEL[2:0]

1 — запуск преобразования регулярных каналов

0 — бит аппаратно сброшен перед началом преобразования.

EXTTRIG (External trigger conversion mode for regular channels): разрешение внешнего триггера, используемого для запуска преобразования регулярной группы каналов

0 — запуск внешним сигналом запрещён

1 — запуск внешним сигналом разрешён.

EXTSEL[2:0] (External event select for regular group): с помощью данного поля выбирается внешнее событие, используемое для запуска начала преобразования регулярной группы каналов. Поле актуально при установленном бите EXTTRIG

Для ADC1 и ADC2 используются следующие события:

000 — Timer1 CC1

001 — Timer1 CC2

010 — Timer1 CC3

011 — Timer1 CC4

100 — Timer 3 TRGO

101 — Timer4 CC4

110 — EXTI line 11/TIM8_TRGO event (TIM8_TRGO доступен только в контроллерах high-density and XLdensity)

111 — SWSTART.

Для ADC3 (если есть) используются следующие события:

000 — Timer3 CC1

001 — Timer2 CC3

010 — Timer1 CC3

011 — Timer8 CC1

100 — TIM8 TRGO

101 — Timer5 CC1

110 — Timer5 CC3

111 — SWSTART.

JEXTTRIG (External trigger conversion mode for injected channels): разрешение внешнего триггера, используемого для запуска преобразования инжектированной группы каналов

0 — запуск внешним сигналом запрещён

1 — запуск внешним сигналом разрешён.

JEXTSEL[2:0] (External event select for injected group): с помощью данного поля выбирается внешнее событие, используемое для запуска начала преобразования инжектированной группы каналов. Поле актуально при установленном бите JEXTTRIG

Для ADC1 и ADC2 используются следующие события:

000 — Timer1 TRGO

001 — Timer1 CC4

010 — Timer2 TRGO

011 — Timer12CC1

100 — Timer 3 CC4

101 — Timer4 TRGO

110 — EXTI line 15/TIM8_CC4 event (TIM8_CC4 доступен только в контроллерах high-density and XLdensity)

111 — SWSTART.

Для ADC3 (если есть) используются следующие события:

000 — Timer1 TRGO

001 — Timer1 CC4

010 — Timer4 CC3

011 — Timer8 CC2

100 — TIM8 CC4

101 — Timer5 TRGO

110 — Timer5 CC4

111 — SWSTART.

ALIGN (Data alignment): бит выравнивания результата в 16 битах регистра.

0 — выравнивание по правому краю

1 — выравнивание по левому краю.

Выравнивание у регулярной и инжектированной групп несколько различается. Данный вопрос мы обсудим, когда будем рассматривать регистр данных.

DMA (Direct memory access mode): данный бит разрешает работу с DMA

0 — режим DMA выключен

1 — режим DMA включен.

RSTCAL (Reset calibration): бит сброса калибровки АЦП. Данный бит устанавливается программно, а сбрасывается аппаратно по окончанию сброса значений калибровки

0 — сброс значений калибровки АЦП завершен

1 — сброс значений калибровки АЦП.

CAL (A/D Calibration): бит запуска калибровки АЦП. Данный бит устанавливается программно при запуске калибровки, а сбрасывается аппаратно по окончанию процесса калибровки

0 — процесс калибровки АЦП завершен

1 — идёт калибровка АЦП.

CONT (Continuous conversion): бит включения непрерывного преобразования

0 — одиночный режим

1 — непрерывный режим.

ADON (A/D converter ON / OFF): бит разрешение работы АЦП

0 — работа АЦП запрещена, АЦП переходит в режим пониженного энергопотребления

1 — работа АЦП разрешена.

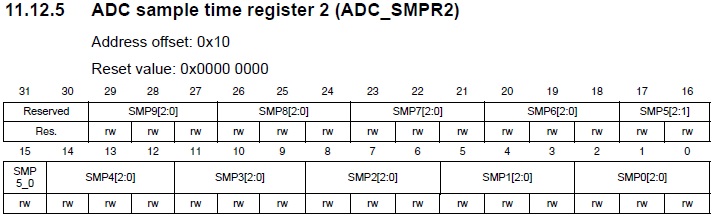

В 3-разрядных битовых полях, организованных для каждого канала, следующих двух регистров задаётся количество тактов между выборками

Настройка битовых полей SMPx[2:0] (Channel x Sample time selection).

В зависимости от комбинаций битов в данных полях мы получим следующие интервалы между выборками

000 — 1,5 цикла

001 — 7,5 цикла

010 — 13,5 цикла

011 — 28,5 цикла

100 — 41,5 цикла

101 — 55,5 цикла

110 — 71,5 цикла

111 — 239,5 цикла.

Так как преобразование длится минимум 12,5 цикла, то минимальный период выборок составит 12,5 + 1,5 = 14 циклов.

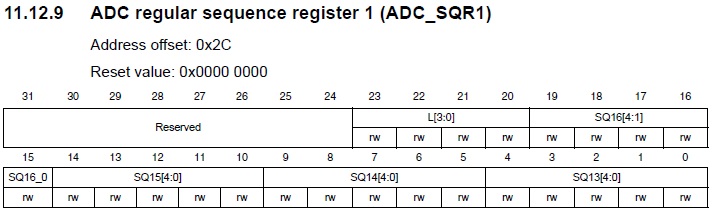

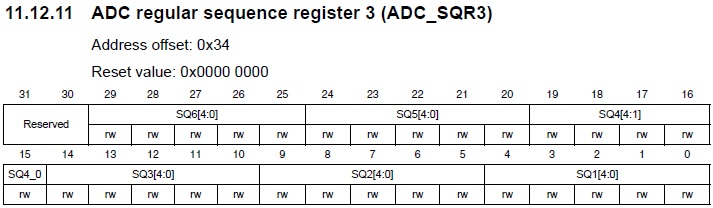

В следующих трёх регистрах — SQR1 — SQR3 мы настраиваем очерёдность сканирования регулярных каналов. Всё это актуально при установленном бите SCAN регистра CR1.

Самое первое битовое поле L[3:0], находящееся в самом первом регистре содержит количество каналов в последовательности для сканирования, а в остальных полях SQx[4:0], имеющихся для каждого номера в последовательности, содержится номер сканируемого канала в данном элементе очереди. После этого каналы сканируются от элемента последоватеьности 1 и далее

Количество преобразований в последовательности.

L[3:0] (Regular channel sequence length): Длина последовательности для сканирования

000 — 1 преобразование

001 — 2 преобразования

…

111 — 16 преобразований.

Далее идут регистры, предназначенные для инжектированных каналов, с которыми мы лучше познакомимся, когда и будем работать с такими преобразованиями.

Поэтому останется у нас только один регистр — регистр данных регулярных преобразований.

В данный регистр записываются данные одного регулярного преобразования

Мы видим здесь 2 поля. Первое — DATA[15:0] — 16 бит данных преобразования, а ещё поле — ADC2DATA[15:0] — поле данных от второго АЦП, если у нас включен режим парной работы двух АЦП. То есть, в данном случае мы получим результат повышенной точности.

Посмотрим, как именно выравниваются данные в случае использования выравнивания по правому и левому краю применительно к регулярной и инжектированной группам

Биты SEXT — это знаковые биты, а биты D11-D0 — биты данных.

Также немаловажным будет знать то, как из сырых данных, находящихся в регистре данных, получить результат в вольтах.

Результат в вольтах, кроме зависимости от результата из регистра, также будет зависеть от опорного напряжения. В нашем случае это будет напряжение питание.

Данный результат рассчитывается следующим образом: V = RAW x Vref / 4095.

В следующей части нашего урока мы настроим проект, проанализируем код инициализации ADC, напишем и испытаем код измерения напряжения с помощью ADC на практике.

Отладочную плату STM32F103C8T6 можно приобрести здесь STM32F103C8T6

Программатор недорогой можно купить здесь ST-Link V2

Переходник I2C to LCD можно приобрести здесьI2C to LCD1602 2004

Логический анализатор 16 каналов можно приобрести здесь

Смотреть ВИДЕОУРОК в RuTube (нажмите на картинку)

Смотреть ВИДЕОУРОК в YouTube (нажмите на картинку)

Добавить комментарий