STM Урок 62. FMC SDRAM. Часть 1

Урок 62

Часть 1

FMC SDRAM

Сегодня мы попробуем поработать с микросхемой памяти SDRAM.

SDRAM — это динамическое оперативное запоминающее устройство, активным элементов каждой ячейки которого является конденсатор. Также обращение к ячейкам памяти происходит не в плоском пространстве, а посредством матрицы, состоящей из строк и колонок. В каждой ячейке данной памяти хранится 1 бит инфорации. По сравнении со статическим вариантом памяти такая память обладает очень большим быстродействием, а также очень малым потреблением энергии.

Представителем такой памяти мы выберем микросхему MT48LC4M32B2 от компании Micron.

Данная память установлена на плате STM32F746G-DISCO, с которой мы очень хорошо знакомы.

Данная память имеет объём 128 мегабит, но так как из 32 контактов обмена данными распаяно в целях экономии только 16, то в данном варианте будет 64, что также немало. Физически получится 8 мегабайт быстрой оперативной памяти.

Для удобства обращения к памяти, так как алгоритм управления ножками таких микросхем не является простым, компания ST Microelectronics подключила данную память, используя технологию FMC, которая позволяет обращаться к данной памяти, используя плоское адресное пространство, не заботясь об уровнях многочисленных управляющих и адресных ножек.

Тем не менее мы все равно немного ознакомимся с организацией работы с данной памяти.

Для этого мы откроем техническую документацию на данную микросхему и, во-первых посмотрим распиновку и назначение отдельных контактов микросхемы. Только это чуть позже. Сначала некоторые технические характеристики, самые, так сказать, основные.

Конфигурация памяти имеет разбивку на 4 банка: 1 мегаадрес по 32 бита (1 бит на каждый контакт шины данных) и таких 4 банка, вот и получаем мы 128 мегабит.

1 мегаадрес получаем мы из расчета матрицы 4096 строк по 256 колонок.

Вот вообщем кратко по организации памяти.

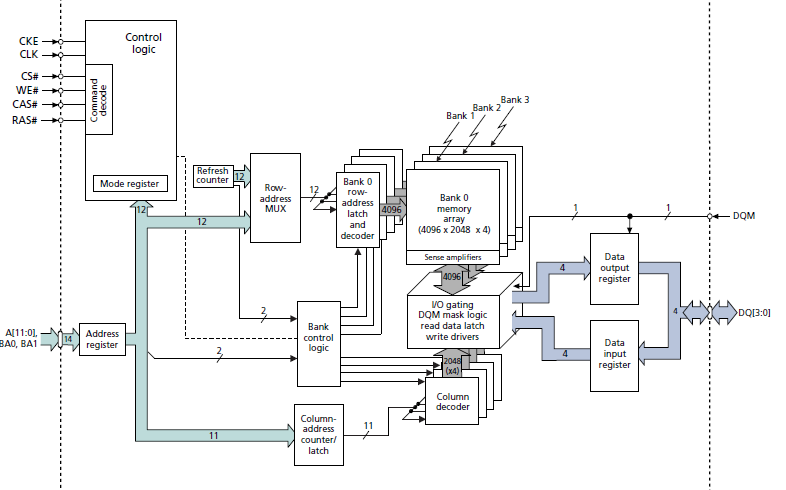

Посмотрим блок-схему нашей микросхемы

Здесь мы уже организацию памяти видим более наглядно. Также мы видим здесь все шины подключения, за исключением шины данных. Вернее она есть, но как-то странно написана.

Шина данных состоит из 32 ножек — это ножки DQ0-DQ31. По этим ножкам, выставляя их в определённое время в определённое состояние, мы записываем информацию в память, а также читаем её с них также в определённое время, снимая их состояния.

Ножки DQM[3:0] отвечают за определённый доступ к данным. Подробно не рассматриваем.

Адресная шина состоит 12 ножек A0-A11. По ней мы обращаемся по определённым адресам к определённым ячейкам памяти, передавая по данным ножкам адрес колонки и адрес строки.

Также к адресному регистру ещё относятся и ножки выбора одного из четырёх банков памяти BA0-BA1.

Также сверху мы ещё наблюдаем ряд ножек, относящимся к командной логике.

CLK — это ножка, которая обеспечивает синхронизацию, собственно, также она называется у многих устройств, требующих синхронизацию.

CKE — ножка, разрешающая синхронизацию.

CS — ножка выбора или Chip Select, необходимая для выбора определённой микросхемы, когда их несколько.

WE — Write Enable, отвечающая за состояние записи или чтения.

CAS — при активизации данной ножки состояние адресной шины расценивается микросхемой, как адрес колонки.

RAS — при активизации данной ножки состояние адресной шины расценивается как адрес строки.

Также существует ряд команд для настройки микросхемы, с которыми мы, возможно и познакомимся в процессе программирования, но возможно нам это и не потребуется, так как все низкоуровневые функции возьмёт на себя FMC.

Можно также немного познакомиться с тем как же всё-таки вообще читаются и пишутся данные. Я думаю, многим это будет интересно. Хотя конечно всё это можно найти, почитав техническую документацию.

Сначала рассмотрим некоторые команды.

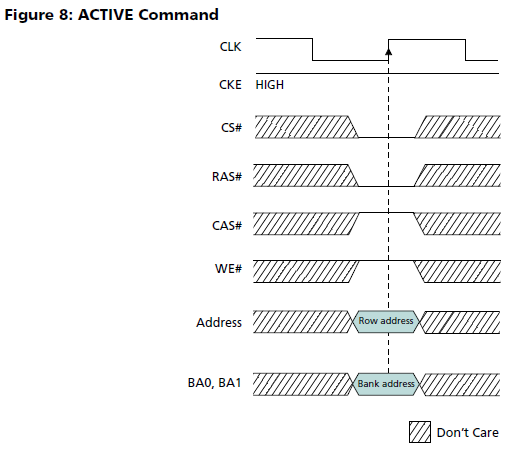

Команда активации

Данная команда инициализируется для того, чтобы выбрать определённый банк и адрес строки.

Следующая после неё команда уже скажет памяти о том, читаем мы с неё или пишем в неё, а также передаст адрес колонки.

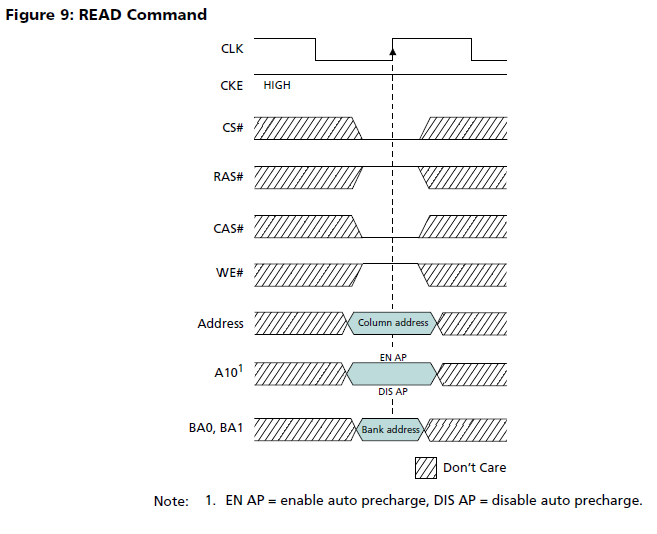

Команда чтения

Здесь мы видим необходимые состояния ножек.

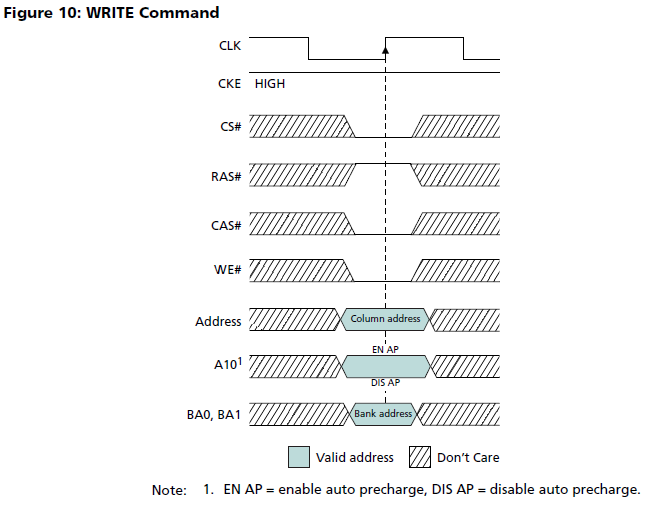

Команда записи

Здесь мы также видим приблизительно ту же картину, единственное отличие — ножка WE в низком состоянии. Вот по её состоянию микросхема и поймёт что мы в неё пишем. В двух последних операциях уже передаётся адрес колонки.

Но это конечно только предварительная подготовка к записи или чтению. Дальше в работу уже вступает шина данных и масса вариантов различных типов доступа — подряд или случайный и ещё несколько интересных вариантов, которые также все описаны в технической документации, которая будет прикреплена к уроку в конце страницы.

Время от времени мы всё равно будем поглядывать и в даташит микросхемы, и отладочной платы, а также будем конечно и к схеме отладочной платы обращаться.

В следующей части занятия мы уже плотно займёмся созданием проекта для решения нашей поставленной задачи — работе с памятью SDRAM с использованием контроллера памяти FMC.

Техническая документация на микросхему SDRAM MT48LC4M32B2

Отладочную плату можно приобрести здесь STM32F746G-DISCOVERY

Смотреть ВИДЕОУРОК в RuTube (нажмите на картинку)

Смотреть ВИДЕОУРОК в YouTube (нажмите на картинку)

Добавить комментарий